Capabilities pointer, 0x34, Interrupt line – Avago Technologies LSI53C895A User Manual

Page 121: 0x3c, Register: 0x34, Register: 0x3c

PCI Configuration Registers

4-13

The host system detects the size of the external memory

by first writing the

register

with all ones and then reading back the register. The

LSI53C895A responds with zeros in all don’t care

locations. The ones in the remaining bits represent the

binary version of the external memory size. For example,

to indicate an external memory size of 32 Kbytes, this

register, when written with ones and read back, returns

ones in the upper 17 bits.

The size of the external memory is set through MAD[3:1].

Please see the section on

for the

possible size encodings available.

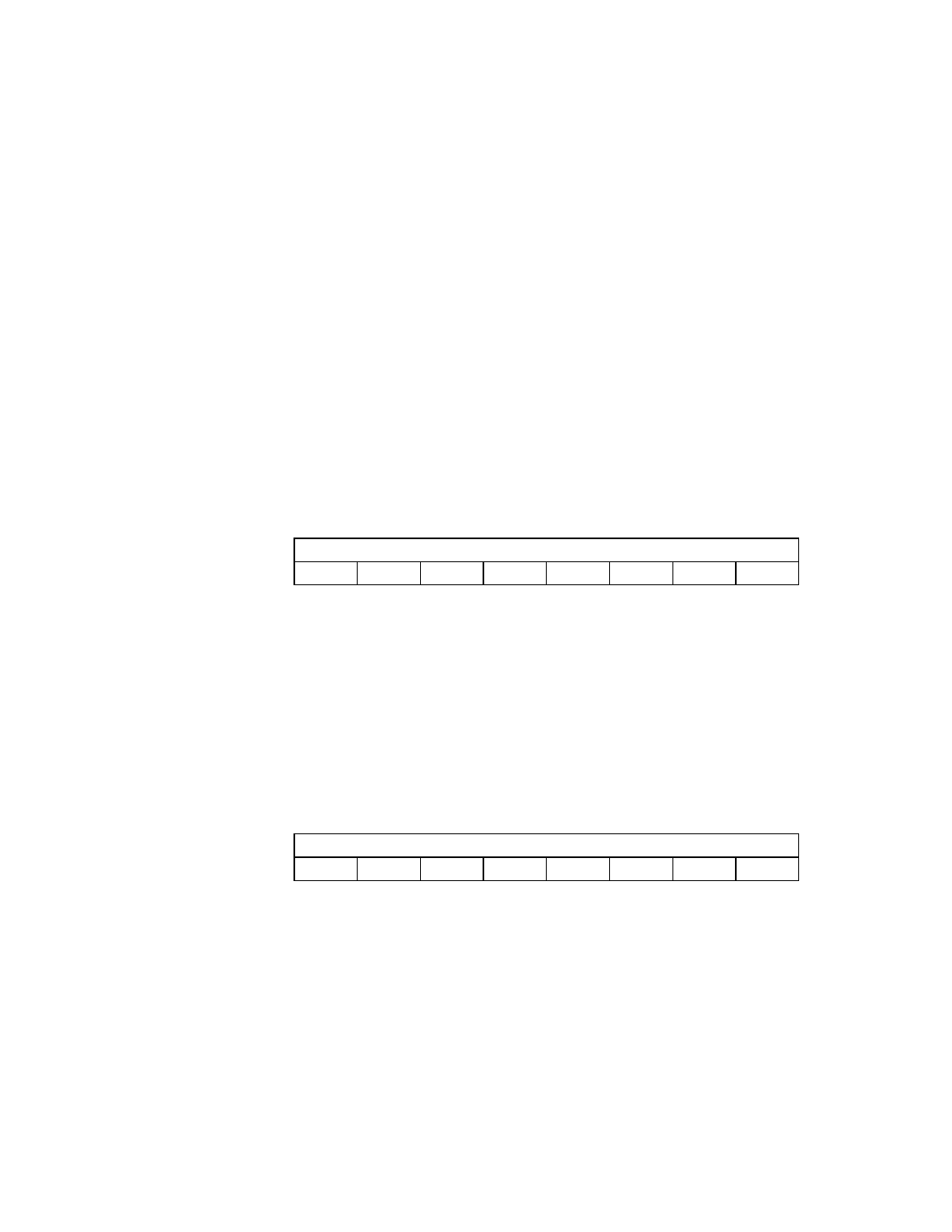

Register:

0x34

Capabilities Pointer

Read Only

CP

Capabilities Pointer

[7:0]

This register indicates that the first extended capability

register is located at offset 0x40 in the PCI Configuration.

Registers: 0x35–0x3B

Reserved

Register: 0x3C

Interrupt Line

Read/Write

IL

Interrupt Line

[7:0]

This register is used to communicate interrupt line routing

information. POST software writes the routing information

into this register as it configures the system. The value in

this register tells which input of the system interrupt

7

0

CP

0

1

0

0

0

0

0

0

7

0

IL

0

0

0

0

0

0

0

0