2 address and data signals, Table 3.3 address and data signals, Address and data signals – Avago Technologies LSI53C895A User Manual

Page 93: Address and, Data signals

PCI Bus Interface Signals

3-5

3.3.2 Address and Data Signals

describes Address and Data signals.

Table 3.3

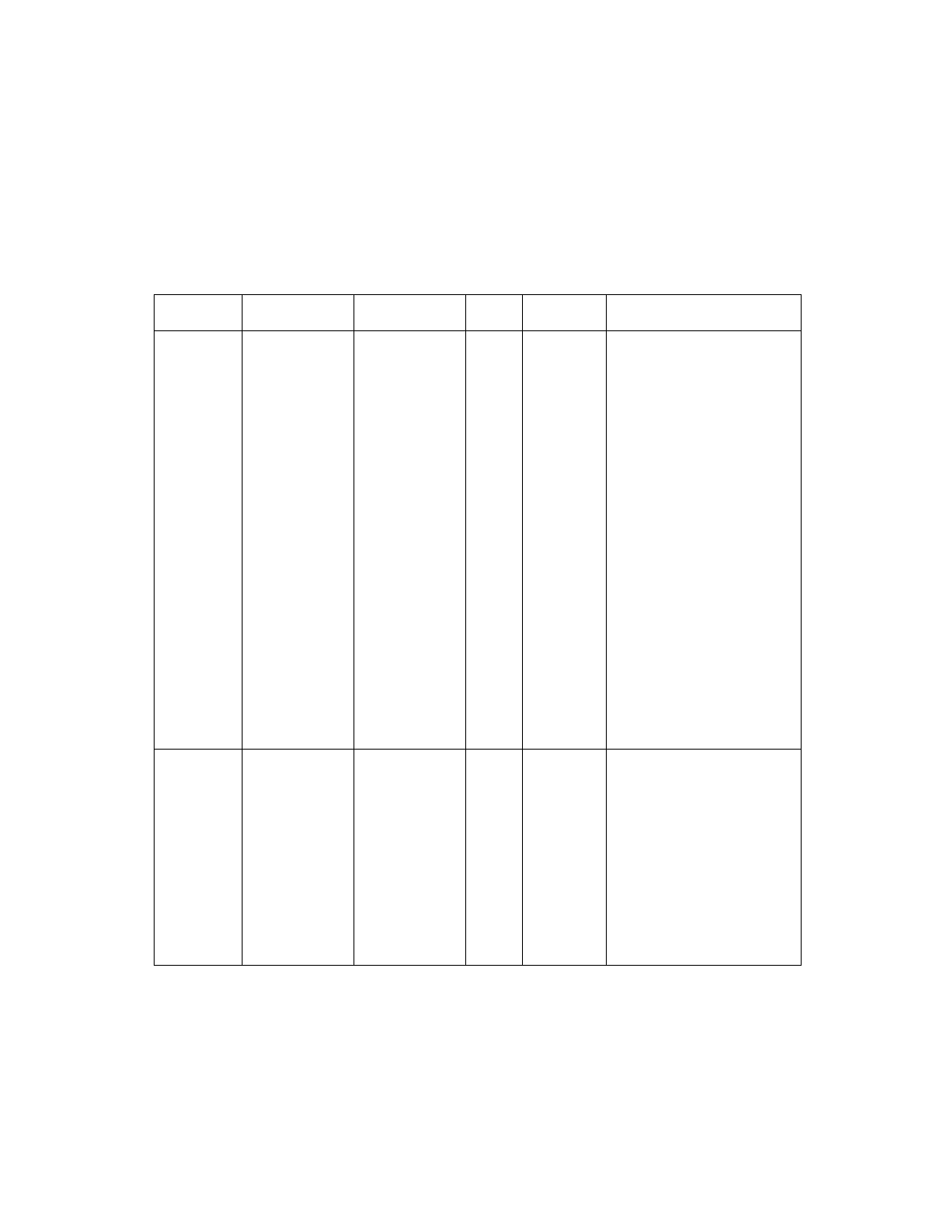

Address and Data Signals

Name

PQFP

BGA Pos

Type

Strength

Description

AD[31:0]

199, 201–204,

3, 5, 6, 10–12,

14–17, 19,

33–35, 37–40,

42, 44, 45, 47,

48, 50, 51, 57,

58

U2, V1, V2,

W1, V3, Y3, V5,

W5, W6, Y6,

V7, W7, Y7, V8,

W8, Y8, V12,

Y13, W13, V13,

Y14, W14, Y15,

W15, Y17,

W17, Y18, V17,

Y19, V18, U18,

V20

T/S

8 mA PCI

Physical Dword Address

and Data are multiplexed on

the same PCI pins. A bus

transaction consists of an

address phase followed by

one or more data phases.

During the first clock of a

transaction, AD[31:0] contain

a 32-bit physical byte

address. If the command is a

DAC, implying a 64-bit

address, a second address

phase is required. During the

first phase, AD[31:0] will

contain the lower 32 bits of

the address followed by a

second phase with AD[31:0]

containing the upper 32 bits

of the address. During

subsequent clocks, AD[31:0]

contain data. PCI supports

both read and write bursts.

AD[7:0] define the least

significant byte, and

AD[31:24] define the most

significant byte.

C_BE[3:0]/

7, 20, 32, 43

Y5, U9, W12,

Y16

T/S

8 mA PCI

Bus Command and Byte

Enables are multiplexed on

the same PCI pins. During

the address phase of a

transaction, C_BE[3:0]/

define the bus command.

During the data phase,

C_BE[3:0]/ are used as byte

enables. The byte enables

determine which byte lanes

carry meaningful data.

C_BE[0]/ applies to byte 0,

and C_BE[3]/ to byte 3.