Normal/fast memory, 128 kbytes) multiple byte access write, Cycle – Avago Technologies LSI53C896 User Manual

Page 320

Advertising

6-52

Specifications

Version 3.3

Copyright © 1998–2003 by LSI Logic Corporation. All rights reserved.

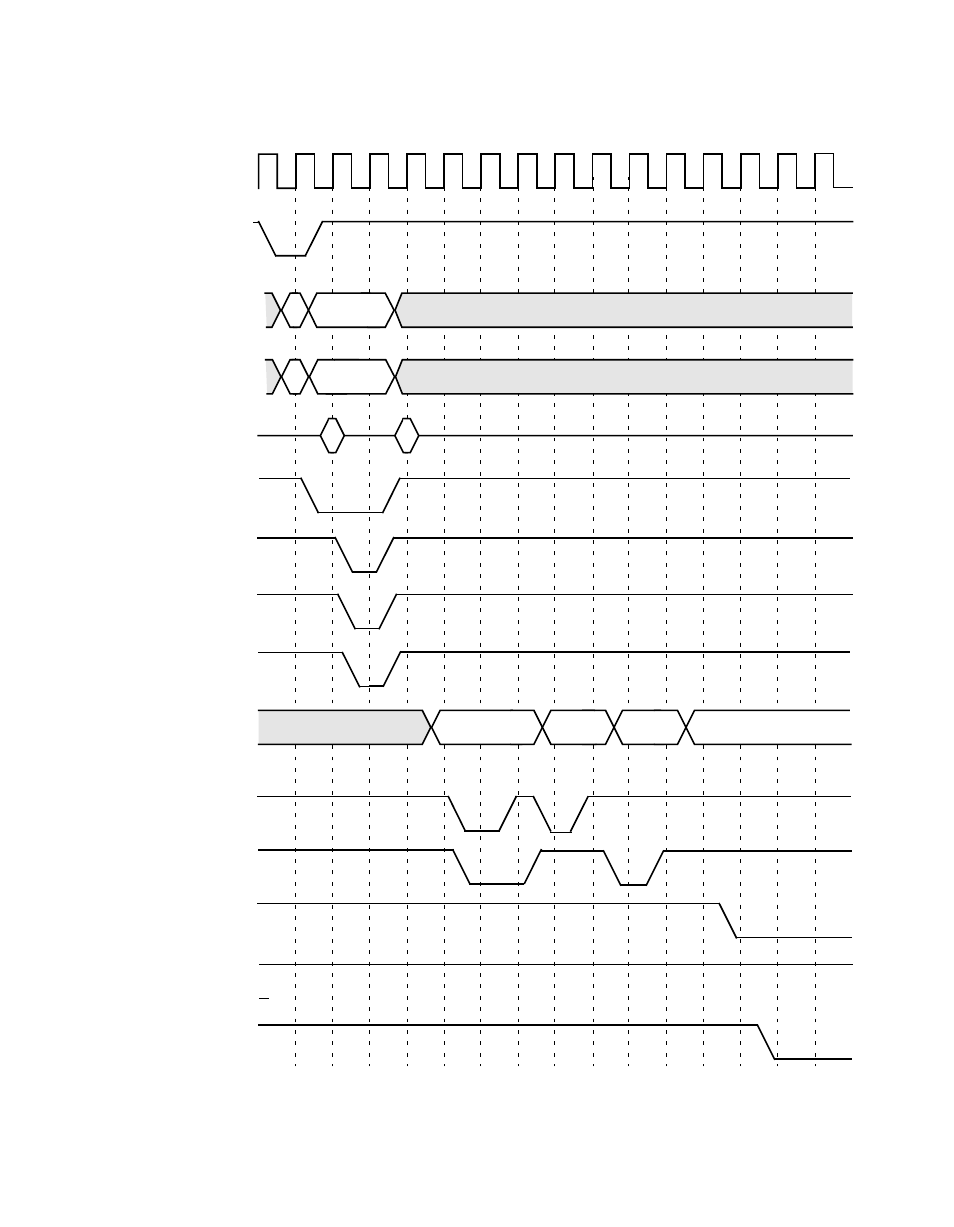

Figure 6.30 Normal/Fast Memory (

≥

128 Kbytes) Multiple Byte Access Write Cycle

CLK

(Driven by System)

PAR

IRDY/

(Driven by Master)

TRDY/

(Driven by LSI53C896)

STOP/

(Driven by LSI53C896)

DEVSEL/

(Driven by LSI53C896)

AD[31:0]

C_BE[3:0]/

(Driven by Master)

FRAME/

(Driven by Master)

MAD

(Driven by LSI53C896)

MAS1/

(Driven by LSI53C896)

MAS0/

(Driven by LSI53C896)

MCE/

(Driven by LSI53C896)

MOE/

(Driven by LSI53C896)

MWE/

(Driven by LSI53C896)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

In

Addr

CMD

In

High Order

Address

Order

Address

Middle

Order

Address

Low

Data Out

Data

In

Byte

Enable

In

(Driven by Master)

(Driven by Master)

Advertising