Stm settings, Etr settings – Altera SoC Embedded Design Suite User Manual

Page 163

• Cycle Accurate – check to create cycle accurate tracing

• Trace capture range – check to enable tracing only a certain address interval

• Start Address, End Address – define the tracing address interval (Used only if the Trace Capture

Range is enabled)

STM Settings

The STM tab allows you to configure the System Trace Macrocell (STM).

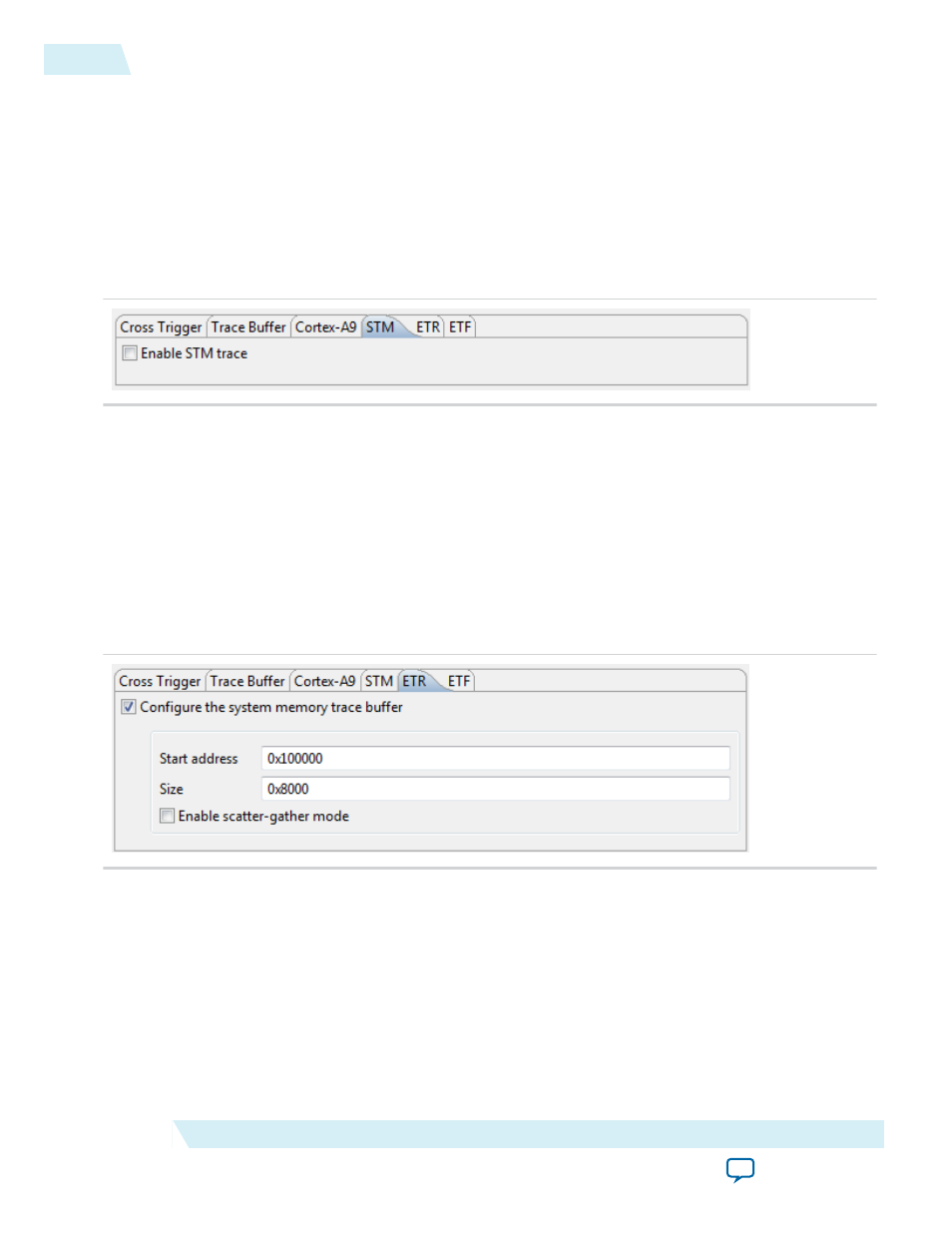

Figure 5-37: DTSL Configuration Editor - STM

Only one option is available:

• Enable STM Trace – check to enable STM tracing.

ETR Settings

The ETR settings allow the configuration of the Embedded Trace Router (ETR) settings.

The Embedded Trace Router is used to direct the tracing information to a memory buffer accessible by

HPS.

Figure 5-38: DTSL Configuration Editor - ETR

The following options are available:

• Configure the system memory trace buffer – check this if the ETR is selected for trace destination on

the Trace Buffer tab

• Start Address, Size – define the trace buffer location in system memory and its size

• Enable scatter-gather mode – use when the OS cannot guarantee a contiguous piece of physical

memory. The scatter-gather table is setup by the operating system using a device driver and is read

automatically by the ETR.

5-38

STM Settings

ug-1137

2014.12.15

Altera Corporation

ARM DS-5 Altera Edition