Reset assert settings – Altera SoC Embedded Design Suite User Manual

Page 179

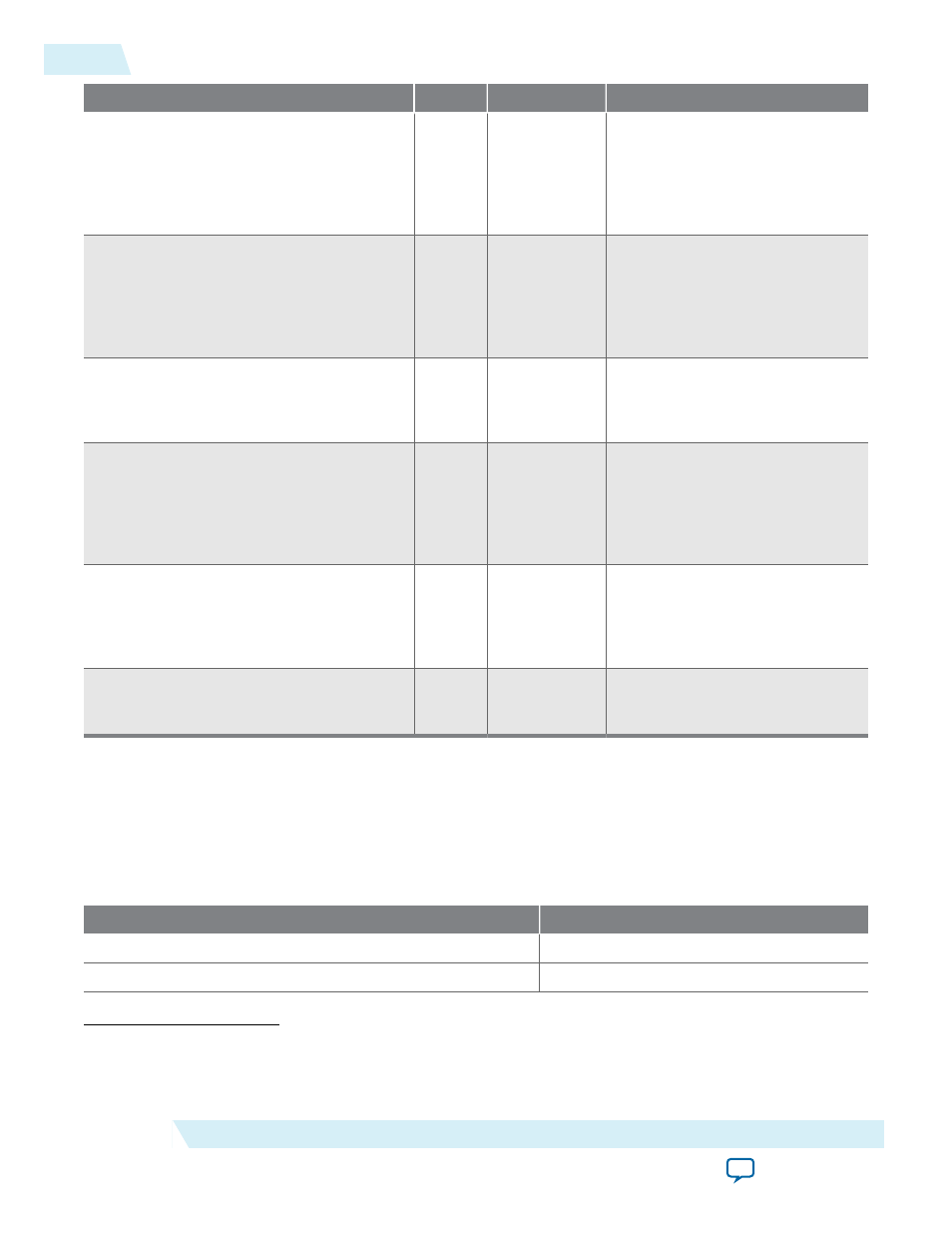

BSP Setting

Type

Default Value

Description

spl.warm_reset_handshake.SDRAM

Boolean True

This setting enables the reset

manager to request that the

SDRAM controller puts the

SDRAM device into self-refresh

mode before asserting warm

reset.

spl.boot.FPGA_MAX_SIZE

Hexadec

imal

0x10000

This setting specifies the

maximum code (.text

and .rodata) size that can fit

within the FPGA. If the code

build is bigger than the specified

size, a build error is triggered.

(5)

spl.boot.FPGA_DATA_BASE

(6)

Hexadec

imal

0xFFFF0000

This setting specifies the base

location for the data region

(.data, .bss, heap and stack) when

execute on FPGA is enabled.

spl.boot.FPGA_DATA_MAX_SIZE

(7)

Hexadec

imal

0x10000

This setting specifies the

maximum data (.data, .bss, heap

and stack) size that can fit within

FPGA. If the code build is bigger

than the specified size, a build

error is triggered.

spl.debug.DEBUG_MEMORY_ADDR

Hexadec

imal

0xFFFFFD00

This setting specifies the base

address for storing preloader

debug information enabled with

the

spl.debug.DEBUG_MEMORY_

WRITE

setting.

spl.debug.DEBUG_MEMORY_SIZE

Hexadec

imal

0x200

This setting specifies the

maximum size used for storing

preloader debug information.

Related Information

on page 7-14

Reset Assert Settings

Table 7-7: spl.reset_assert.<

peripheral_name

>

BSP Setting

Default Value

spl.reset_assert.DMA

False

spl.reset_assert.GPIO0

False

(5)

.text and .rodata are default memory sections defined by the linker tool in the GCC tool chain.

(6)

.data and .bss are default memory sections defined by the linker tool in the GCC tool chain.

(7)

.data and .bss are default memory sections defined by the linker tool in the GCC tool chain.

7-14

Reset Assert Settings

ug-1137

2013.05.03

Altera Corporation

HPS Preloader User Guide