Altera SoC Embedded Design Suite User Manual

Page 178

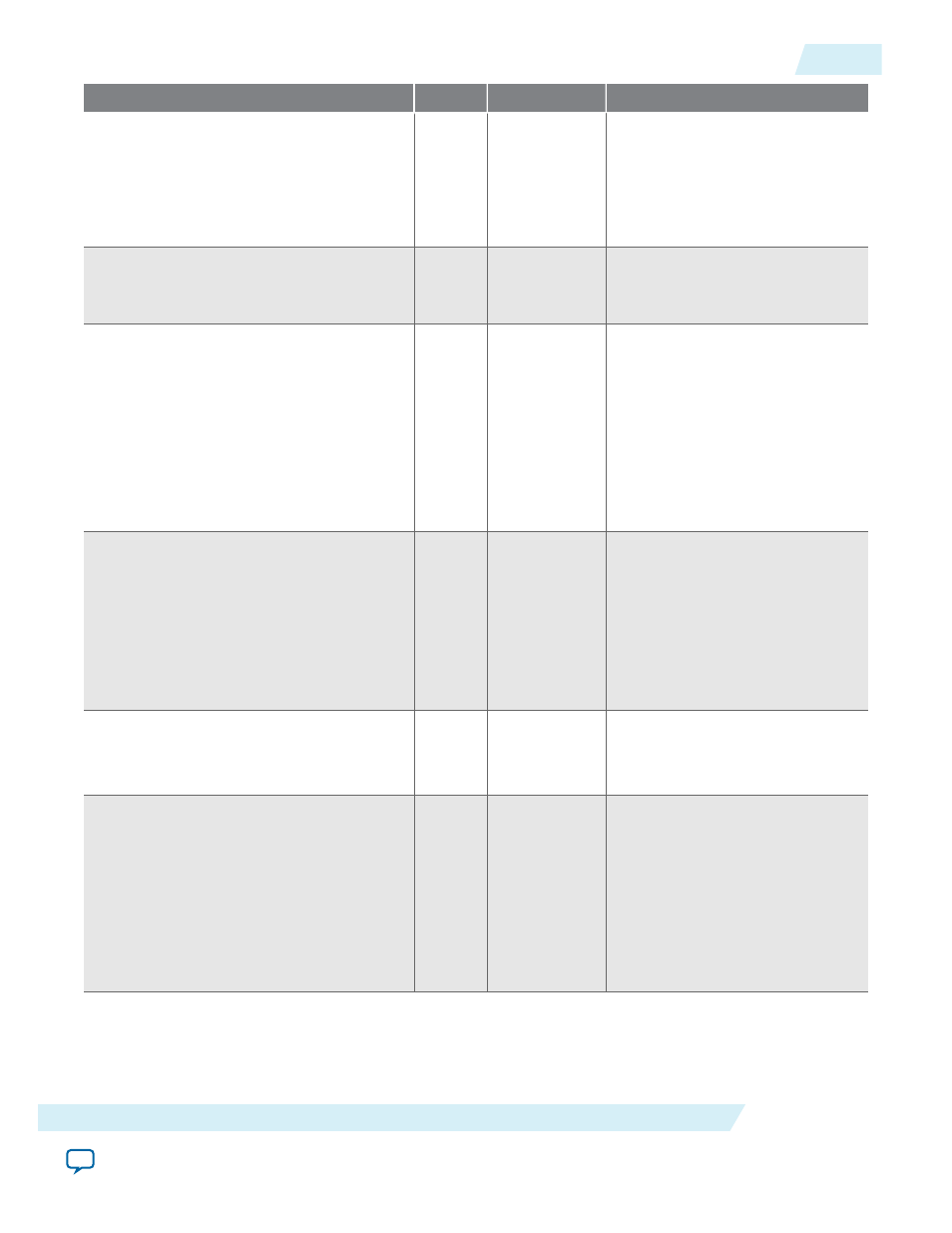

BSP Setting

Type

Default Value

Description

spl.debug.HARDWARE_DIAGNOSTIC

Boolean False

This setting enables hardware

diagnostic support, enabling

hardware to read from and write

to the SDRAM to ensure

hardware is working; the status is

reported in the console.

spl.debug.SKIP_SDRAM

Boolean False

The preloader skips SDRAM

initialization and calibration

when this setting is enabled.

spl.performance.SERIAL_SUPPORT

Boolean True

This setting enables UART print

out support, enabling preloader

code to call printf() at runtime

with debugging information.

stdout output from printf() is

directed to the UART. You can

view this debugging information

by connecting a terminal

program to the UART specified

peripheral.

spl.reset_assert.<peripheral_name>

Boolean Refer to

on page 7-14

This setting forces the device to

remain under reset state. You

can include multiple instances of

spl.reset_

assert.<peripheral_name>

to

hold multiple peripherals in

reset. You must ensure the

debugger does not read registers

from these components.

spl.warm_reset_handshake.FPGA

Boolean True

This setting enables the reset

manager to perform handshake

with the FPGA before asserting a

warm reset.

spl.warm_reset_handshake.ETR

Boolean True

This setting enables the reset

manager to request that the

Embedded Trace Router (ETR)

stalls the Advanced eXtensible

Interface (AXI) master and waits

for the ETR to finish any

outstanding AXI transactions

before asserting a warm reset of

the L3 interconnect or a debug

reset of the ETR.

ug-1137

2013.05.03

Available BSP Settings

7-13

HPS Preloader User Guide

Altera Corporation