Altera SoC Embedded Design Suite User Manual

Page 86

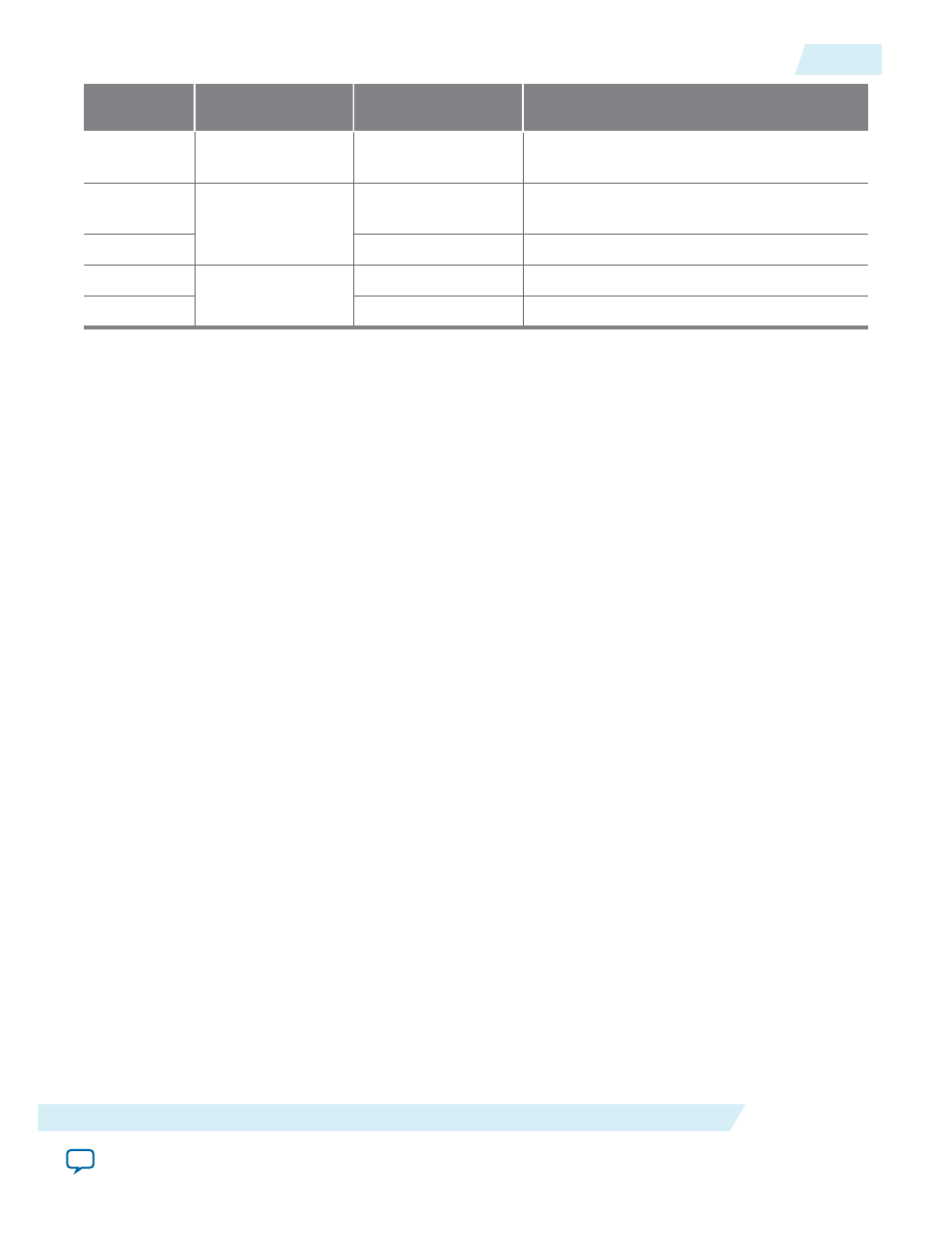

Sequence

Sample Application

Function

Used Hardware

Libraries APIs

Description

12

socfpga_bridge_

cleanup

alt_bridge_uninit

Deinitialize bridges

13

socfpga_fpga_

cleanup

alt_fpga_control_

disable

Disable control of FPGA

14

alt_fpga_uninit

Close the FPGA driver

15

socfpga_dma_

cleanup

alt_dma_channel_free Deallocate the DMA channel

16

alt_dma_uninit

Close the DMA driver

Getting Started with Peripheral Register Visibility

The ARM DS-5 Altera Edition allows you to specify the peripheral IP register descriptions using .svd files.

The .svd files are resulted from the hardware project compilation using ACDS.

The .svd files contain the description of both HPS peripheral registers, such as UART, EMAC, and timers;

and the Soft IP peripheral registers residing on FPGA side.

This section presents the necessary steps in order to view the HPS registers and the Soft IP registers using

the Getting Started with Hardware Library example.

Note: The soft IP register descriptions are not generated for all soft IP cores. Do not expect to have

registers for all the cores they use on FPGA. Some may have it, some may not.

1. Perform the steps described in the Getting Started with Hardware Library section up to and including

configuring the USB Blaster connection.

2. In the Eclipse IDE, click Run > Debug Configurations... to open the Debug Configurations dialog

box.

3. In the Debug Configurations dialog box, go to the Files panel and under the Files panel:

a. Select Add peripheral description files from directory from the drop down box

b. Use the browse File System button to browse to the folder <SoC EDS Folder>\examples\hardware

\cv_soc_devkit_ghrd\soc_system\synthesis. This is where the .svd file generated by Quartus II is

located.

ug-1137

2014.12.15

Getting Started with Peripheral Register Visibility

4-67

Getting Started Guides

Altera Corporation