Preloader compilation, Configuring fpga from preloader, Preloader compilation -15 – Altera SoC Embedded Design Suite User Manual

Page 180: Configuring fpga from preloader -15

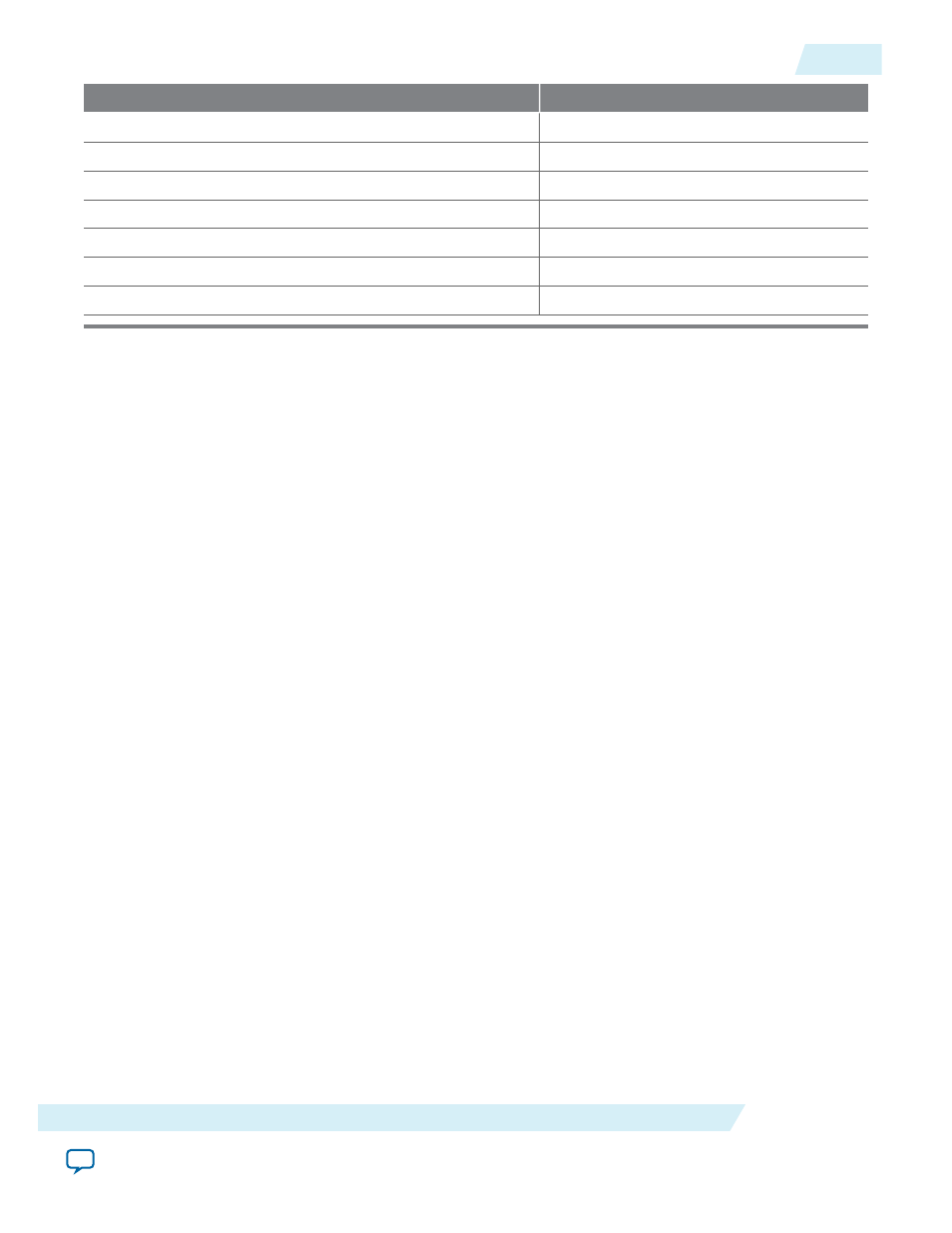

BSP Setting

Default Value

spl.reset_assert.GPIO1

False

spl.reset_assert.GPIO2

False

spl.reset_assert.L4WD1

False

spl.reset_assert.OSC1TIMER1

False

spl.reset_assert.SDR

False

spl.reset_assert.SPTIMER0

False

spl.reset_assert.SPTIMER1

False

Preloader Compilation

The makefile created by the PSP generator compiles the preloader sources and generates a preloader

image. The makefile performs the following tasks:

• Copies the generic preloader source code into

<bsp directory>/uboot-socfpga

• Copies the generated BSP files and hardware handoff files to the source directory in

<bsp_directory>/

uboot-socfpga/board/altera/socfpga_<device>

• Configures the compiler tools to target an SoC FPGA

• Compiles the source files in

<bsp directory>/uboot-socfpga

with the user-specified cross compiler

(specified in the BSP settings) and stores the generated preloader binary files in

<bsp_directory>/uboot-

socfpga/spl

• Converts the preloader binary file to a preloader image,

<bsp_directory>/preloader-mkpimage.bin

, with

the mkpimage tool

The mkpimage tool is part of the SoC EDS. It inserts the correct header information and creates an Altera

boot-ROM compatible image of the preloader. You can run the make utility in the command shell to

compile the preloader in the BSP directory. The makefile contains the following targets:

• make all – compiles the preloader

• make clean – deletes

preloader-mkpimage.bin

from the <bsp directory>

• make clean-all – deletes <bsp directory>, including the source files in the directory

Related Information

Configuring FPGA from Preloader

The Preloader has the ability to configure the FPGA by using configuration data stored in one of the

following two locations:

• specific address in QSPI Flash

• specific file name on a SD/MMC FAT Partition

In order to configure the FPGA, an RBF file needs to be used. The RBF file is obtained by converting a

SOF file to RBF by using the Quartus II Programmer.

ug-1137

2013.05.03

Preloader Compilation

7-15

HPS Preloader User Guide

Altera Corporation