Alis-2 – Wavecom W61PC V7.5.0 User Manual

Page 119

WAVECOM Decoder W61PC/LAN Manual V7.5

Transmission Modes

109

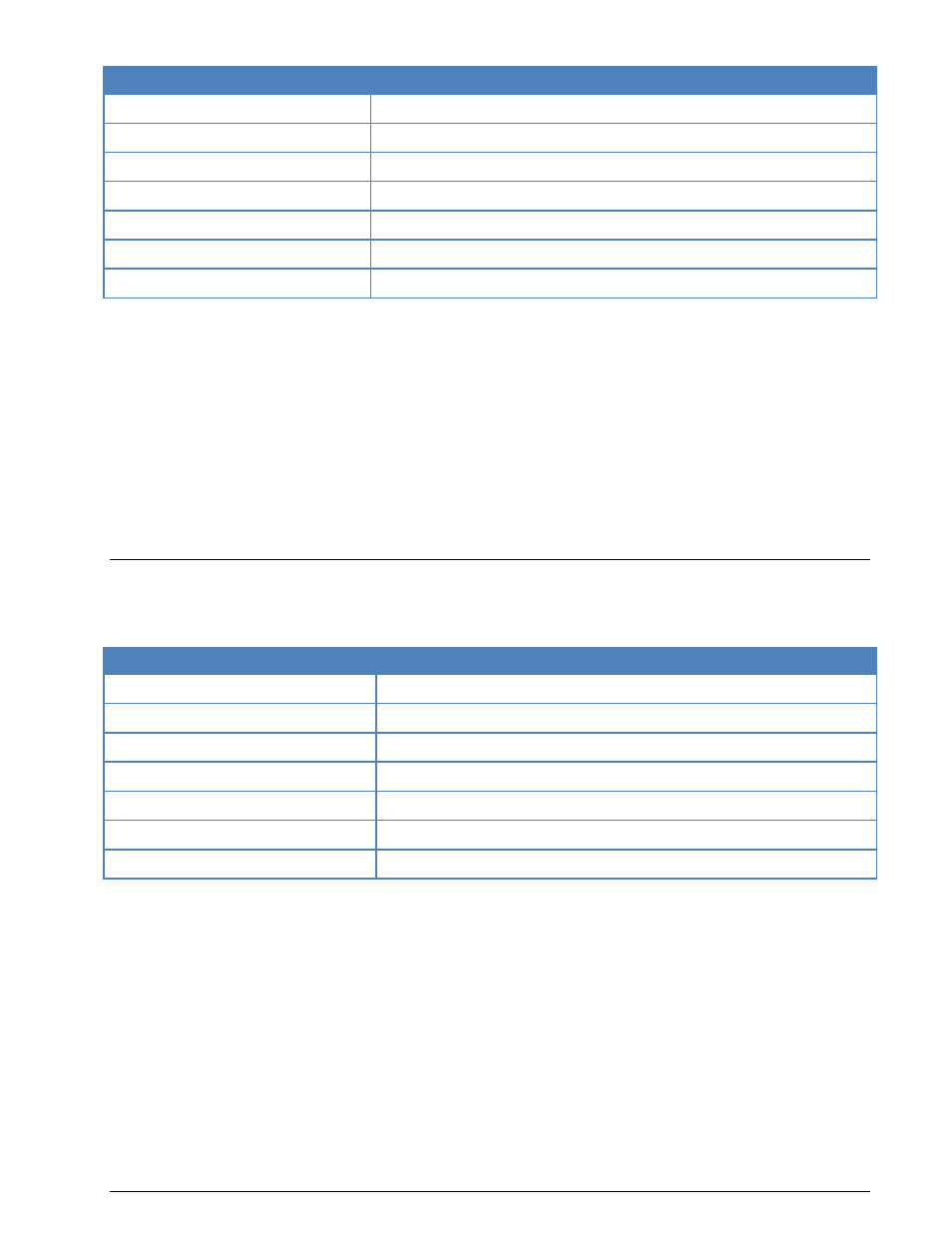

Parameter

Value

Frequency range

HF

Operation modes

FSK, Simplex ARQ

Modulation

FSK

Symbol rate

228.66 Bd, variable 30-650 Bd

Receiver settings

DATA, CW, LSB or USB

Input format(s)

AF, IF

Additional Info

ITA-2 with block coding

The transmission block of the standard ARQ system consists of 2 identification bits, 30 data bits and 16

CRC bits. Data transmission is transparent for ALIS. Known systems are however structured around six

ITA-2 characters.

The two identification bits indicate one of four possible system states. The CRC checksum enables detec-

tion and correction of transmission errors.

The acknowledgement block is 16 bits in length. The total transmit-receive cycle for ALIS is 111 bits,

which corresponds to a duration of 485.4 ms. An error free transmission is equivalent to a terminal baud

rate of 100 Baud.

The ALIS system automatically determines the optimal operating frequency after having received a CALL

command. The station then sends a synchronization word, address, block counter and a status word. The

receiving station correlates this bit sequence and synchronizes itself. If the data transmission link fails,

ALIS will search for a new frequency to re-establish the link.

ALIS-2

ALIS-2 (Automatic Link Set-up) is a simplex system operating with a baud rate of 240.82 baud. ALIS-2 is

described in the "Report of the CCIR 1990, Fixed Service at Frequencies below about 30 MHz" of the ITU.

Parameter

Value

Frequency range

HF

Operation modes

Simplex ARQ

Modulation

MFSK-8

Symbol rate

240.82 Bdd

Receiver settings

DATA, CW, LSB or USB

Input format(s)

AF, IF

Additional Info

ITA-5

ALIS-2 is 8-FSK modulated. The tone spacing is 240 Hz, and the tone duration is 4.15254 ms. The trans-

mission block consists of 55 tri-bits, resulting in 165 bits per frame. In addition to the preamble of 21 bits,

each block contains 126 data bits. The preamble includes an identification code, allowing different systems

to be identified.

Two identification bits signal four operational states: traffic, idle, RQ and binary data transfer. The 16-bit

CRC-checksum serves the detection of transmission errors and error correction purposes.

The overall transmission and receive cycle of ALIS-2 is 354 bits, which is equivalent to 490 ms. In case of

an error-free data transmission, the terminal bit rate is 720 bit/s.

ALIS-2 almost always uses the ITA-5 ASCII alphabet.

The ALIS-2 system automatically determines the optimum operating frequency after having received a

CALL command. The station then sends a synchronization word, address, block counter and a status word.

The receiving station correlates this bit sequence and synchronizes itself. If the transmission link is inter-

rupted, ALIS-2 will search for a new frequency to re-establish the link.