Rlc (ix+d) – Zilog Z08470 User Manual

Page 227

Advertising

UM008007-0715

Z80 Instruction Description

Z80 CPU

User Manual

215

RLC (IX+d)

Operation

Op Code

RLC

Operand

(IX+d)

Description

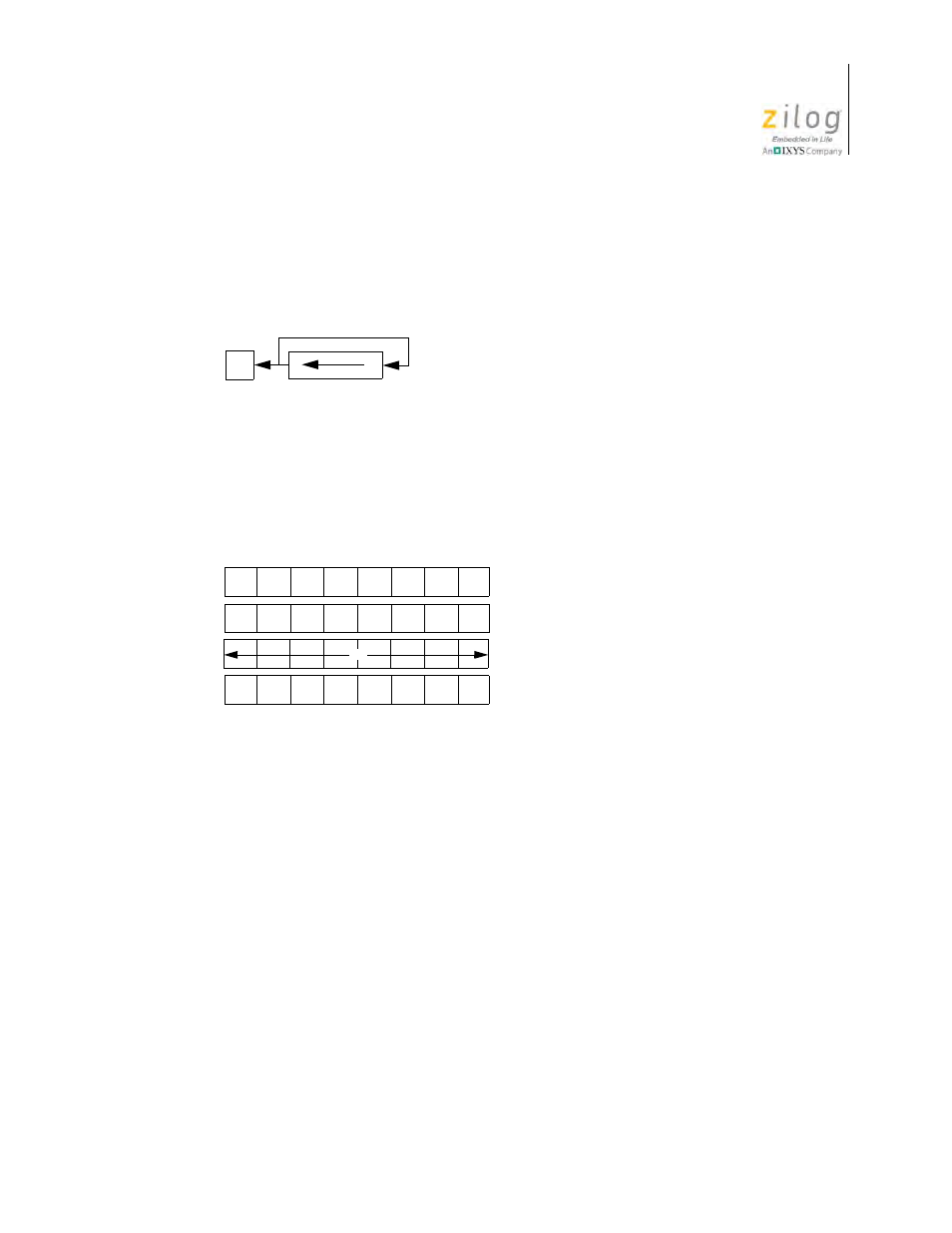

The contents of the memory address specified by the sum of the contents of Index Register

IX and the two’s-complement displacement integer, d, are rotated left 1 bit position. The

contents of bit 7 are copied to the Carry flag and also to bit 0. Bit 0 is the least-significant

bit.

Condition Bits Affected

S is set if result is negative; otherwise, it is reset.

Z is set if result is 0; otherwise, it is reset.

H is reset.

P/V is set if parity even; otherwise, it is reset.

N is reset.

M Cycles

T States

4 MHz E.T.

6

23 (4, 4, 3, 5, 4, 3)

5.75

CY

7

0

(IX+d)

1

1

1

0

1

1

0

1

DD

1

1

0

1

1

0

0

1

CB

0

0

0

1

0

1

0

0

06

d

Advertising