Zilog Z08470 User Manual

Page 307

UM008007-0715

Z80 Instruction Description

Z80 CPU

User Manual

295

INI

Operation

(HL) ← (C), B ← B – 1, HL ← HL + 1

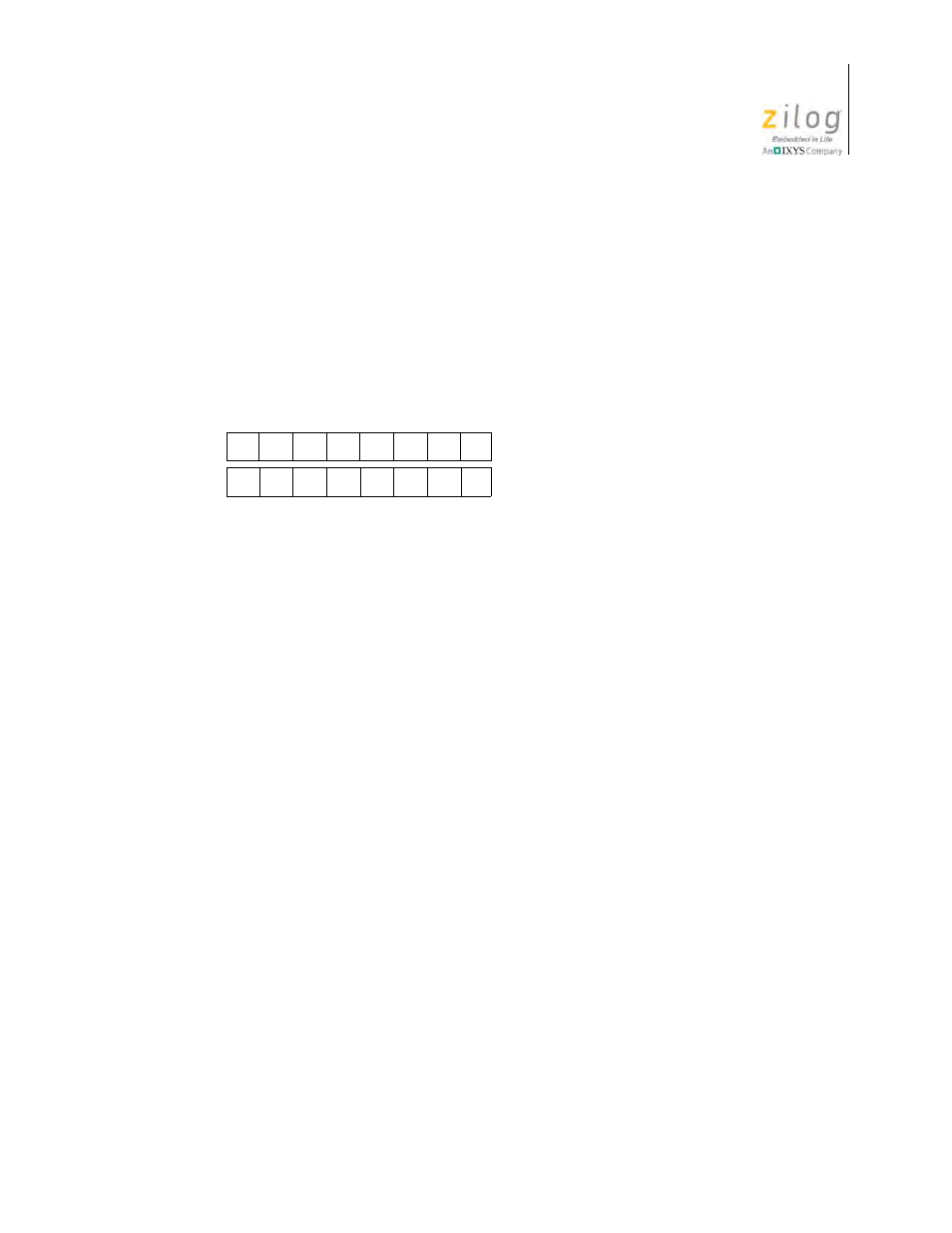

Op Code

INI

Operands

None.

Description

The contents of Register C are placed on the bottom half (A0 through A7) of the address

bus to select the I/O device at one of 256 possible ports. Register B can be used as a byte

counter, and its contents are placed on the top half (A8 through A15) of the address bus at

this time. Then one byte from the selected port is placed on the data bus and written to the

CPU. The contents of the HL register pair are then placed on the address bus and the input

byte is written to the corresponding location of memory. Finally, the byte counter is decre-

mented and register pair HL is incremented.

Condition Bits Affected

S is unknown.

Z is set if B – 1 = 0; otherwise it is reset.

H is unknown.

P/V is unknown.

N is set.

C is not affected.

M Cycles

T States

4 MHz E.T.

4

16 (4, 5, 3, 4)

4.00

1

1

0

0

1

1

1

1

ED

1

0

0

1

0

0

1

0

A2