Artesyn CPCI-6200 Installation and Use (May 2015) User Manual

Page 190

Memory Maps and Addresses

CPCI-6200 Installation and Use (6806800J66E)

190

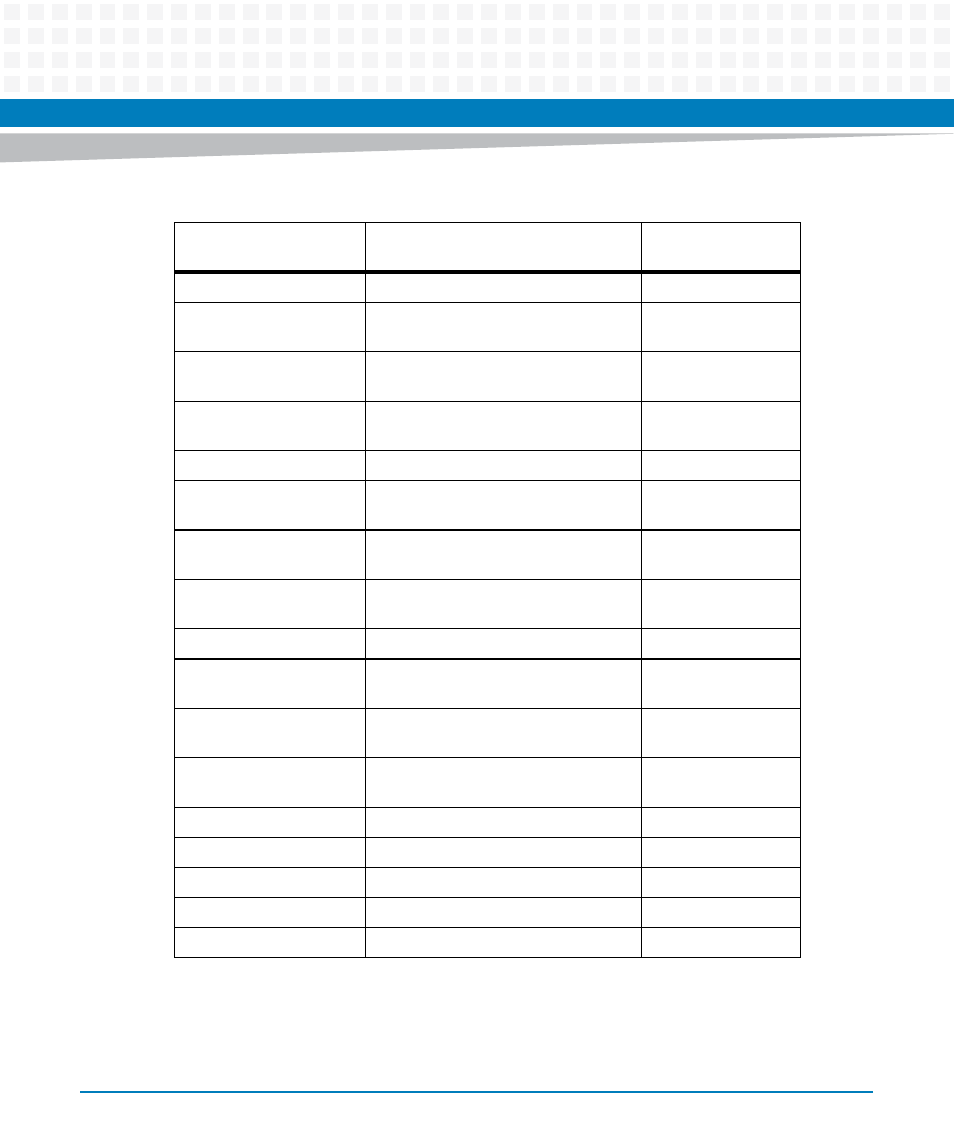

F202 001C

2

Reserved

5

F202 0020

2

External PLD Tick Timer 2 Control

Register

5

F202 0024

2

External PLD Tick Timer 2 Compare

Register

5

F202 0028

2

External PLD Tick Timer 2 Counter

Register

5

F202 002C

2

Reserved

5

F202 0030

2

External PLD Tick Timer 3 Control

Register

5

F202 0034

2

External PLD Tick Timer 3 Compare

Register

5

F202 0038

2

External PLD Tick Timer 3 Counter

Register

5

F202 003C

2

Reserved

5

F202 0040

2

External PLD Tick Timer 4 Control

Register

5

F202 0044

2

External PLD Tick Timer 4 Compare

Register

5

F202 0048

1

External PLD Tick Timer 4 Counter

Register

5

F202 004C–F202 FFFF

2

Reserved

5

F203 0000

3

Nand Chip 1 Data Register

1

F203 0001–F203 7FFF

Reserved

1

F203 8000

3

Nand Chip 2 Data Register

1

F203 8001–F203 FFFF

Reserved

1

1. Reserved for future implementation.

2. 32-bit write only

3. Byte read/write capable

Table 8-4 System I/O Memory Map (continued)

Address

Definition

LBC Bank/Chip

Select