3 compare registers, Table 8-56, Tick timer compare registers – Artesyn CPCI-6200 Installation and Use (May 2015) User Manual

Page 219

Memory Maps and Addresses

CPCI-6200 Installation and Use (6806800J66E)

219

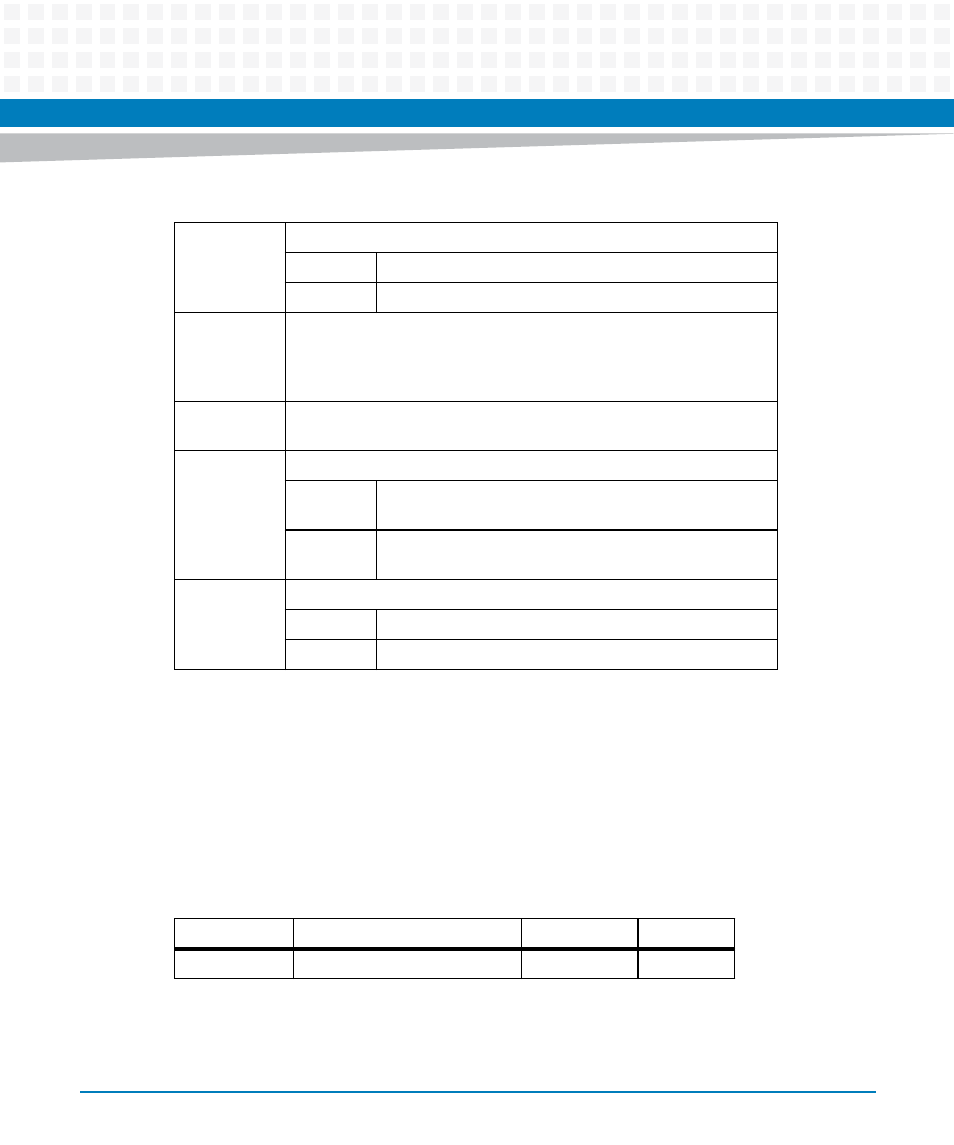

8.4.27.3 Compare Registers

Tick Timer 1 Compare Register—0xF202_0014 (32 bits)

Tick Timer 2 Compare Register —0xF202_0024 (32 bits)

Tick Timer 3 Compare Register—0xF202_0034 (32 bits)

Tick Timer 4 Compare Register—0xF202_0044 (32 bits)

EN_INT

Enable Interrupt

1

Interrupt is enabled.

0

Interrupt is disabled.

OVF

Overflow bits. These bits are the output of the overflow counter. The

overflow counter is incremented each time the tick timer sends an

interrupt to the local bus interrupter. The overflow counter can be

cleared by writing a 1 to the COVF bit.

COVF

Clear overflow bits. The overflow counter is cleared when a 1 is written

to this bit.

COC

Clear counter on compare

1

Counter is reset to 0 when it compares with the compare

register.

0

Counter is not reset when it compares with the compare

register.

ENC

Enable counter

1

Enable the counter increments.

0

Disable the counter increments.

Table 8-55 Tick Timer Control Field Definition (continued)

Table 8-56 Tick Timer Compare Registers

Bit

Field

Operation

Reset

31:0

Tick Timer Compare Value

R/W

0