Transfer size, Reference clock frequency, Transfer size –3 reference clock frequency –3 – Altera SerialLite II IP Core User Manual

Page 26: Size= 2

Chapter 3: Parameter Settings

3–3

Physical Layer Configuration

January 2014

Altera Corporation

SerialLite II MegaCore Function

User Guide

The data rates for an individual Arria II GX device are limited to the respective speed

grades, refer to

Transfer size

The Transfer size parameter defines many important characteristics of the MegaCore

function variation. Transfer size determines the number of contiguous data columns

and the internal data path width per lane, where:

■

A transfer size of 1 equates to an internal data path of 8 bits (Recommended for

less than 2.5 Gbps)

■

A transfer size of 2 equates to an internal data path of 16 bits (Recommended for

less than or equal to 3.125 Gbps)

■

A transfer size of 4 equates to an internal data path of 32 bits (only available for

Stratix IV FPGA with transfer size greater than 3.125 Gbps, and must be used

when the data rate exceeds 5 Gbps)

A transfer size determines the width of the SERDES block, where:

■

A transfer size of 1 equates to a 10 bit-wide SERDES block

■

A transfer size of 2 equates to a 20 bit-wide SERDES block

■

A transfer size of 4 equates to a 40-bit wide SERDES block

Reference Clock Frequency

The Reference Clock Frequency parameter defines the frequency of the reference

clock for the Arria II GX or Stratix IV internal transceiver. Valid values change with

the data rate but the reference input clock frequency must be within 50 MHz and 622

MHz.

■

The general formula to determine frequency:

Frequency = p×Data Rate/(2×m), where p = 1 or 2, and m = 4, 5, 8, 10, 16, 20, or 25

Condition for frequency to be valid: (50×p) < Frequency < 622

■

This parameter is only applicable if you chose Arria II GX or Stratix IV devices.

Stratix V

TSIZE= 1, 2

TSIZE= 2

TSIZE= 2

TSIZE= 4

Note to

(1) Symmetric mode (p_RX_NUM_LANES == p_TX_NUM_LANES) only.

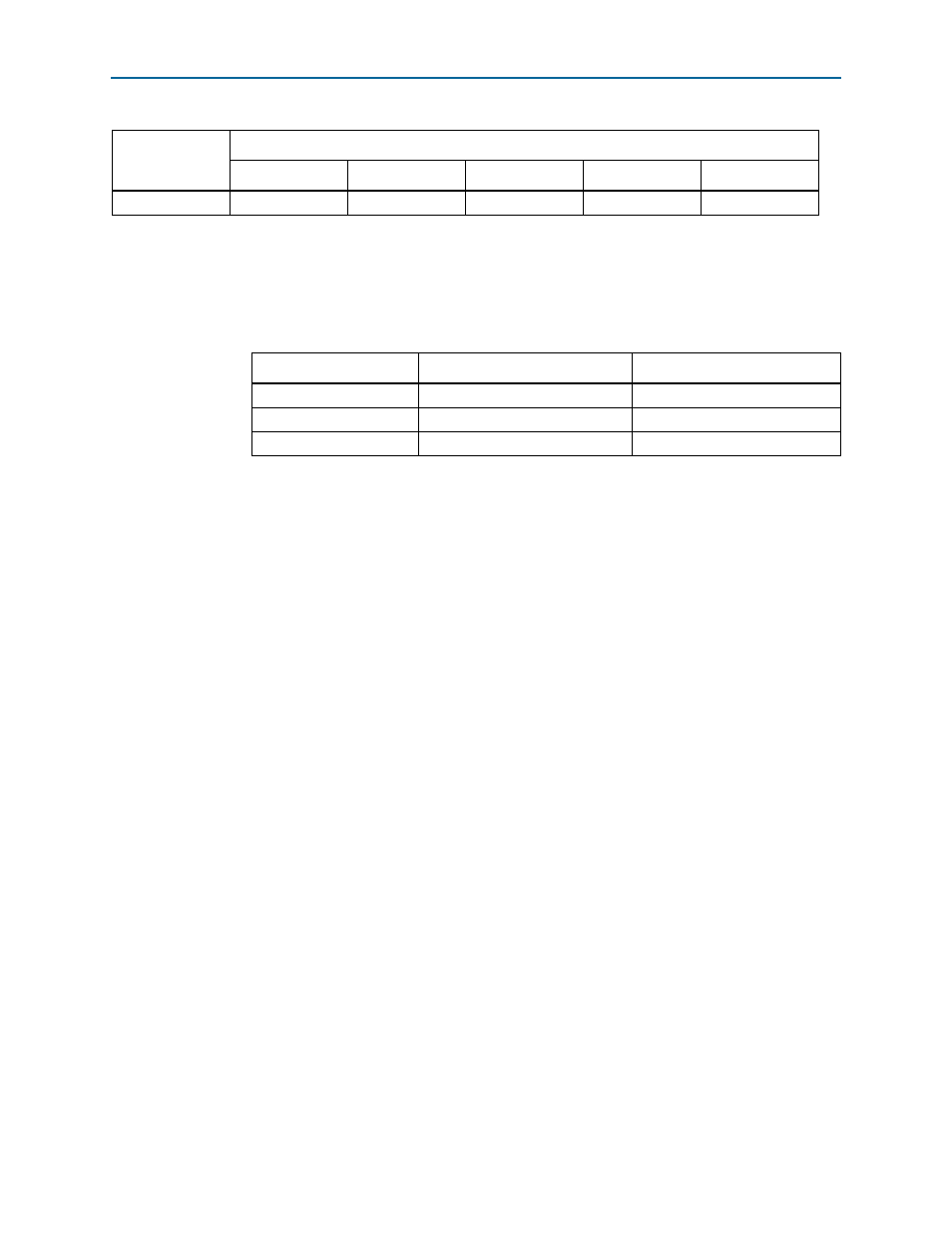

Table 3–2. Data Rate Dependencies on Transfer Size (Part 2 of 2)

Devices

Data Rate

2.5 Gbps

3.125 Gbps

3.75 Gbps

5 Gbps

6.375 Gbps

Table 3–3. Arria II GX Speed Grade-Data Rate Limits

Device Speed Grade

Minimum Data Rate (Mbps)

Maximum Data Rate (Mbps)

C4

600 3,750

C5

600 3,125

C6

600 3,125