Xcvr – Altera SerialLite II IP Core User Manual

Page 62

4–8

Chapter 4: Functional Description

Clocks and Data Rates

SerialLite II MegaCore Function

January 2014

Altera Corporation

User Guide

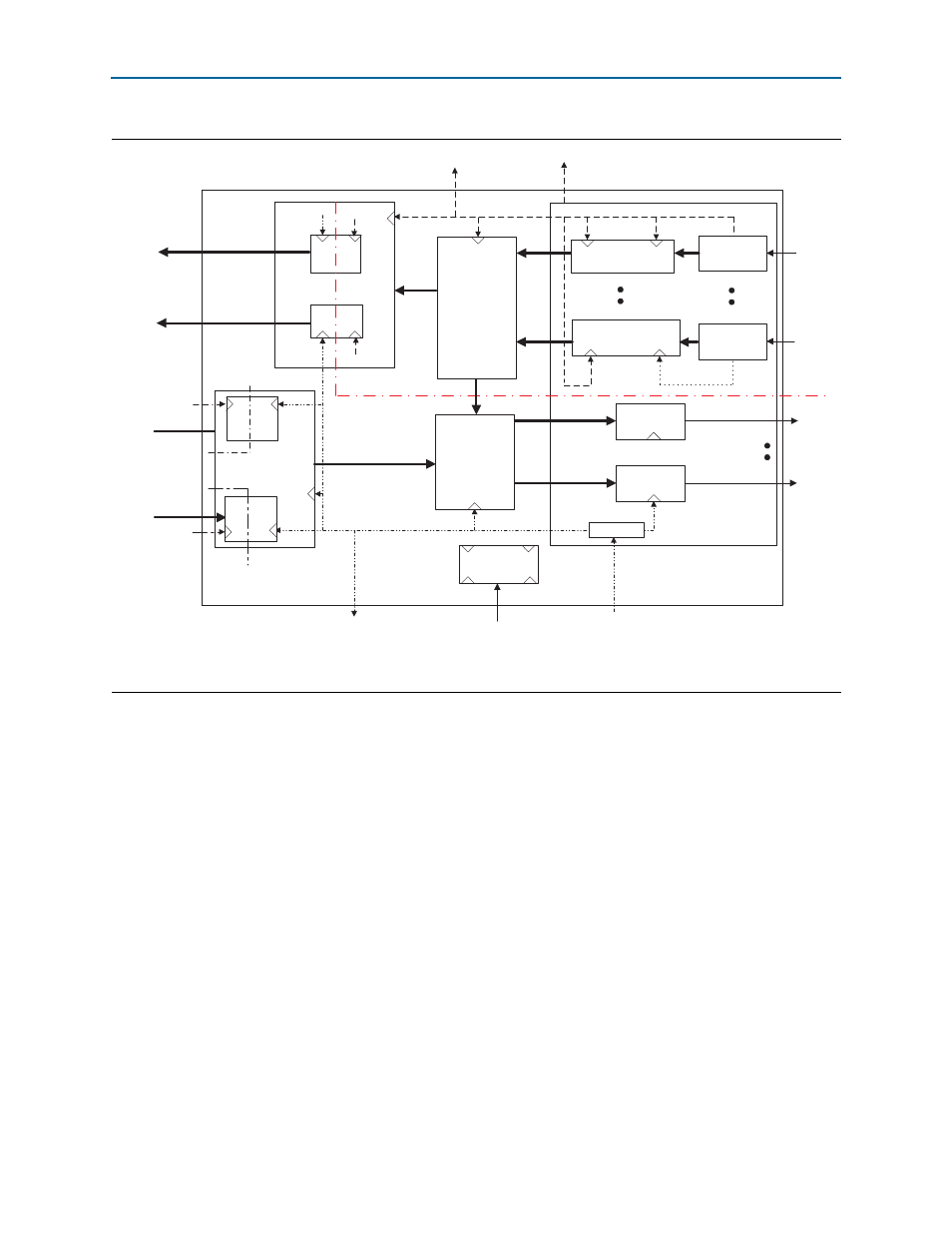

Figure 4–7. No Receiver FIFO Buffers Clock Structure

Note to

(1) Individual recovered clocks (one per channel).

slite2_top

XCVR

TX Core

n-bit

n-bit

RX Core

n-bit

#n SLITE2

High

Speed

Links

#m SLITE2

High

Speed

Links

Atlantic

Atlantic

Atlantic

Regular

(tx_coreclock

domain)

Priority

Regular

PComp_FIFO_0

Byte

serializer

Byte

serializer

PComp_FIFO_n-1

Byte

deserializer

Byte

deserializer

n-bit

txhpp_clk

txrdp_clk

rcvd_clk0

rcvd_clkn-1

tx_coreclock

RREFCLK

mreset_n

Reset Sync

tx_coreclock

rcvd_clk_out[n-1:0]

(1)

Freq Off

Removal

Freq Off

Removal

ATLFIFO

ATLFIFO

rrefclk

rrefclk

Atlantic

Priority

(tx_coreclock

domain)

Word Aligner (&

Training Pattern

Detection),

[Link State

Machine]

Training

Generator [Link

State Machine]

trefclk

TXPLL

tx_coreclock

tx_coreclock

tx_coreclock

tx_coreclock