Features, Features –2 – Altera SerialLite II IP Core User Manual

Page 7

1–2

Chapter 1: About This MegaCore Function

Features

SerialLite II MegaCore Function

January 2014

Altera Corporation

User Guide

shows the level of support offered by the SerialLite II MegaCore function to

each Altera device family.

Features

■

Physical layer features

■

622 Mbps to 6.375 Gbps per lane

■

Single or multiple lane support (up to 16 lanes)

■

8-, 16-, or 32-bit data path per lane

■

Symmetric, asymmetric, unidirectional/simplex or broadcast mode

■

Optional payload scrambling

■

Full-duplex or self-synchronizing link state machine (LSM)

■

Channel bonding scalable up to 16 lanes

■

Synchronous or asynchronous operation

■

Automatic clock rate compensation for asynchronous use

■

±100 and ±300 parts per million (ppm)

■

Link layer features

■

Atlantic

™

interface compliant

■

Support for two user packet types: data packet and priority packet

■

Optional packet integrity protection using cyclic redundancy code (CRC-32 or

CRC-16)

■

Optional link management packets

■

Retry-on-error for priority packets

■

Individual port (data/priority) flow control

■

Unrestricted data and priority packet size

■

Support for TimeQuest timing analyzer

■

Polarity reversal

■

Lane order reversal

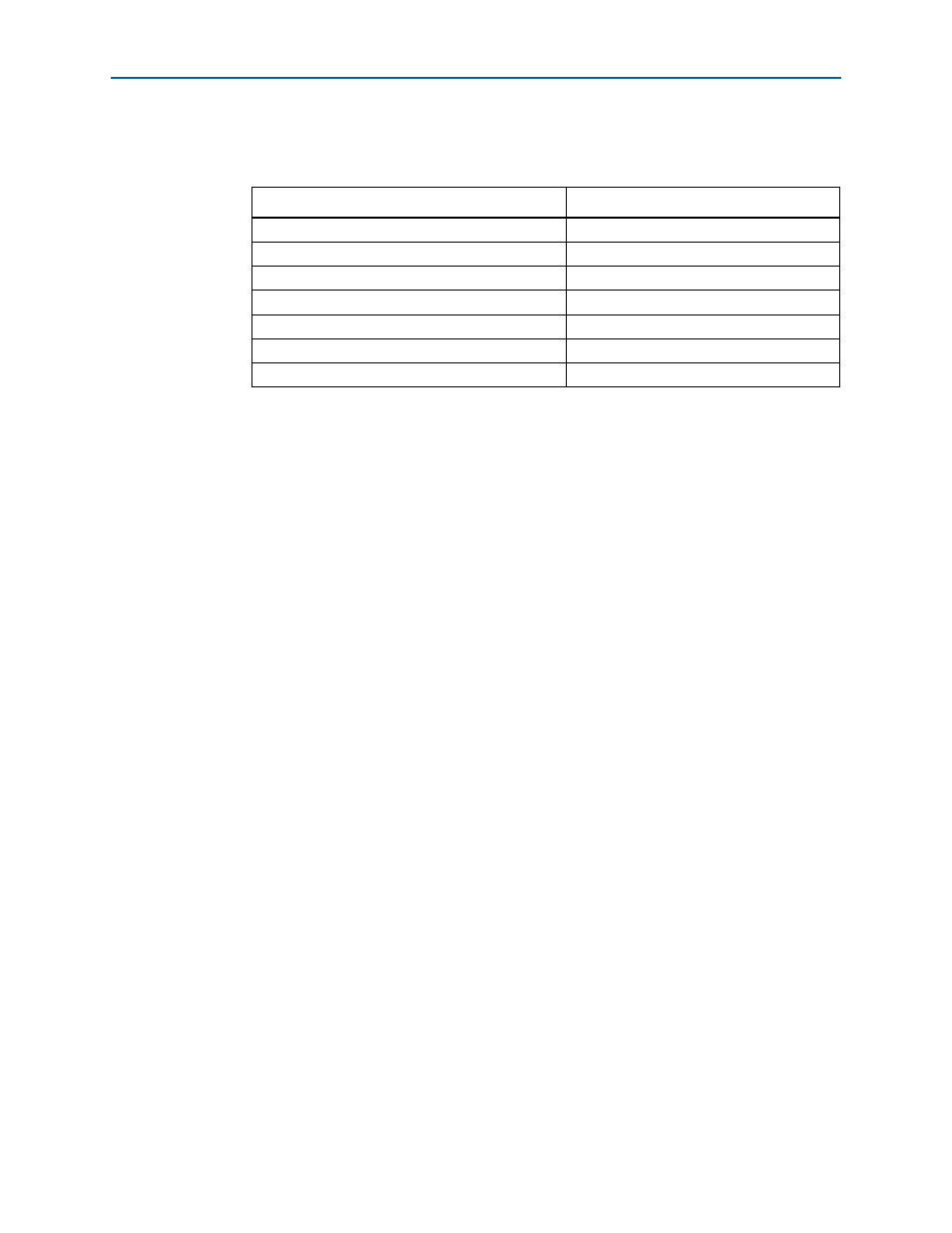

Table 1–2. Device Family Support

Device Family

Support

Arria

®

II GX

Final

Arria V

Preliminary

Arria V GZ

Preliminary

Cyclone

®

V

Preliminary

Stratix

®

IV

Final

Stratix V

Preliminary

Other device families

No support