Design consideration, Compilation, Design consideration –19 – Altera SerialLite II IP Core User Manual

Page 73: Compilation –19

Chapter 4: Functional Description

4–19

MegaCore Configuration for Arria V, Cyclone V, and Stratix V Devices

January 2014

Altera Corporation

SerialLite II MegaCore Function

User Guide

MegaCore Configuration for Arria V, Cyclone V, and Stratix V Devices

The supported features for the SerialLite II MegaCore function in Arria V, Cyclone V,

and Stratix V devices are the same with the Stratix IV GX devices except for the hard

transceiver features. Since there is no hard transceiver in this configuration, you need

to instantiate the Custom PHY IP core and integrate both cores in your design. You

can find the Custom PHY IP core in the following directory in the MegaWizard

Plug-In Manager: Installed Plug-Ins > Interfaces > Transceiver PHY > Custom PHY

<version>

.

lists the Custom PHY IP core blocks and the respective data rate that the

SerialLite II MegaCore function utilizes for this configuration.

f

For more information about the Custom PHY IP core, refer to the

.

Design Consideration

When you instantiate the SerialLite II MegaCore function and Custom PHY IP core,

you must apply the following considerations to create a working design.

Compilation

If you use Tcl constraints to make assignments for the SerialLite II MegaCore function,

you must perform the following actions:

■

Identify the Custom PHY IP core clock node

■

Set the Custom PHY IP core reference clock frequency accordingly in the .sdc file

for design integration between the SerialLite II MegaCore function and Custom

PHY IP core

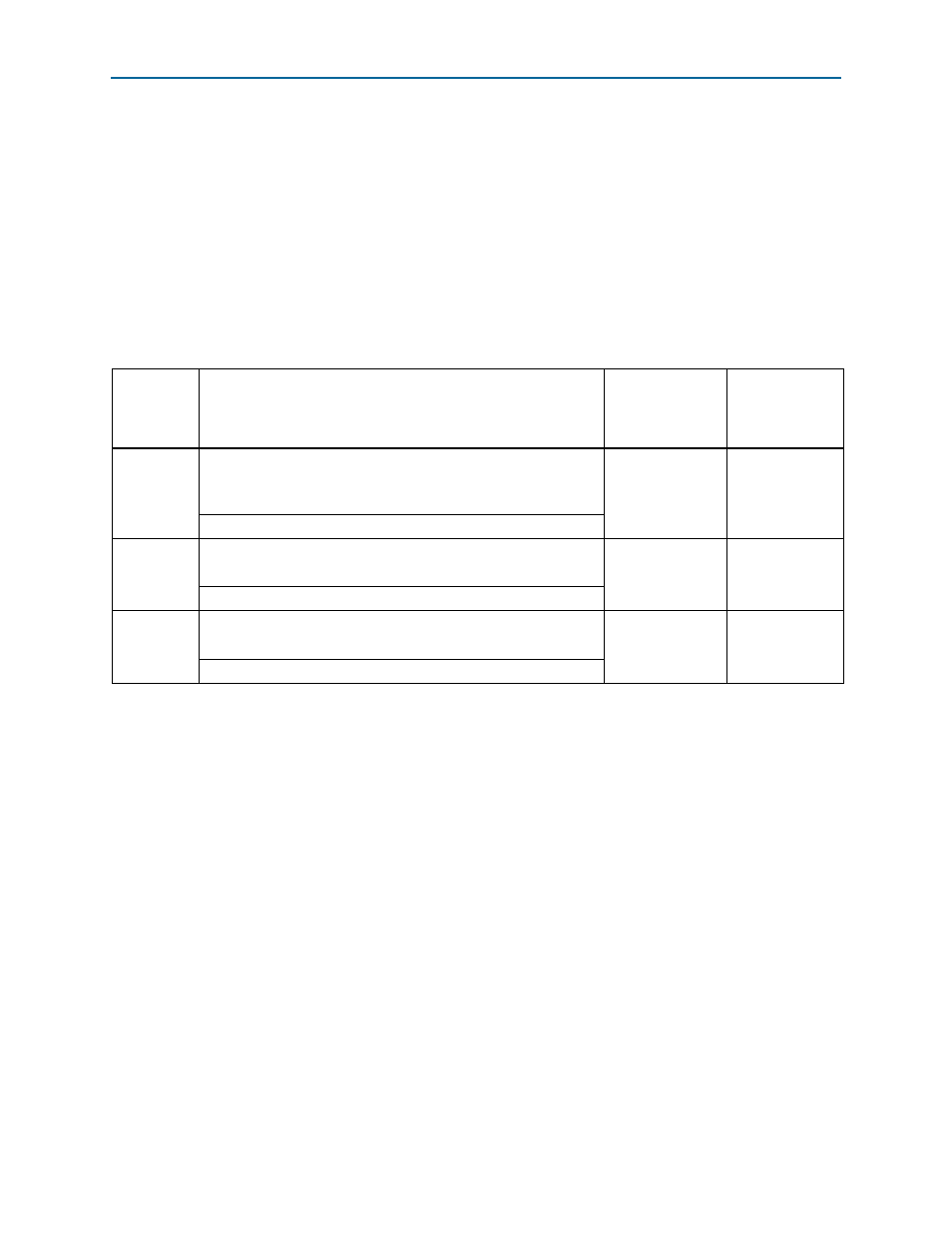

Table 4–2. Custom PHY IP Core Blocks and Data Rate Used by SerialLite II MegaCore Function

FPGA Fabric

Transceiver

Interface

Width

Blocks Enabled

Data Rate (Mbps)

for Arria V GZ/

Arria V GX/

Stratix V

Data Rate (Mbps)

for Cyclone V

32

(TSIZE = 4)

Word alignment mode: Manual

/Automatic synchronization state

machine

Word alignment pattern: 10'h17c

3,126 to 6,375

3,126 to 5,000

8B/10B encoder/decoder

16

(TSIZE = 2)

Word alignment mode: Automatic synchronization state machine

Word alignment pattern: 10'h17c

1,000 to 5,000

1,000 to 3,750

8B/10B encoder/decoder

8

(TSIZE = 1)

Word alignment mode: Automatic synchronization state machine

Word alignment pattern: 10'h17c

622 to 2,500

622 to 1,875

8B/10B encoder/decoder

Notes to

(1) Assert the rx_enapatternalign register in Custom PHY through the Avalon-MM interface to trigger another

alignment when synchronization is lost.

(2) Applicable only for Arria V GZ and Stratix V devices.