Altera SerialLite II IP Core User Manual

Page 75

Chapter 4: Functional Description

4–21

MegaCore Configuration for Arria V, Cyclone V, and Stratix V Devices

January 2014

Altera Corporation

SerialLite II MegaCore Function

User Guide

f

For more information about the Custom PHY IP core ports, refer to the

.

Extra Signals Between SerialLite II MegaCore and Custom PHY IP Core

The SerialLite II MegaCore function includes new signals to interface with the

Custom PHY IP core for data communication.

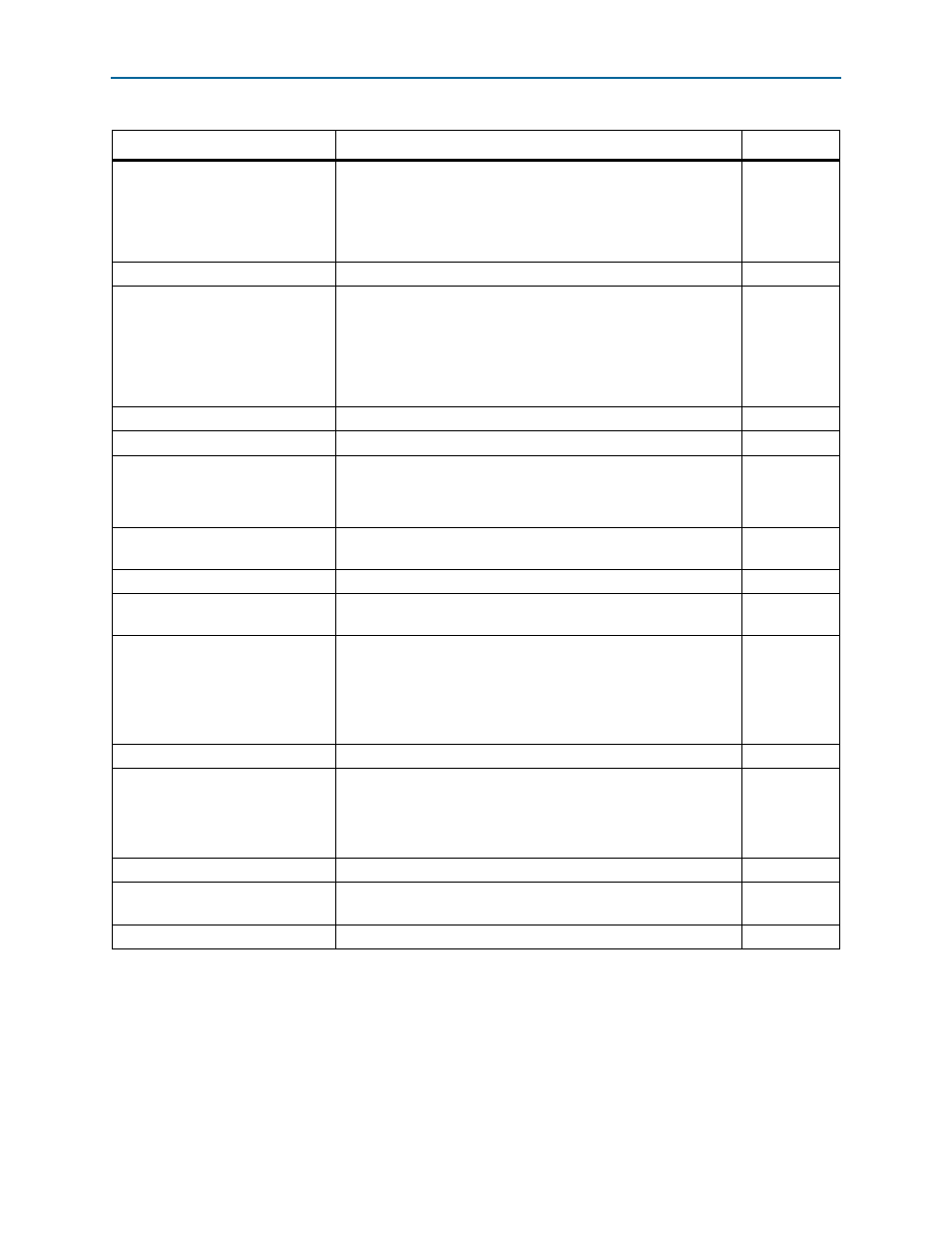

Create tx_coreclkin port

Provides transceiver clock output to the tx_coreclk signal in the

SerialLite II MegaCore.

For Arria V, Cyclone V, and Stratix V designs with more than 1

channel, connect transceiver PHY tx_clkout(0) to

tx_coreclkin (N-1:0)

.

Required

Create rx_recovered_clk port

Provides a recovered clock output for the transceiver.

Off

Create optional ports

Provide the following ports:

■

tx_forceelecidle

■

rx_is_lockedtoref

■

rx_is_lockedtodata

■

rx_signaldetect

Optional

Avalon data interfaces

Enables support for Avalon-Streaming (ST) interface.

Optional

Enable embedded reset controller

Enables the controller to reset the transceiver.

Required

Create optional word aligner status

ports

Provide the following word aligner status ports for the transceiver:

■

rx_syncstatus

■

rx_patterndetect

Optional

Enable run length violation checking

Enables run length violation check to the err_rr_rlv signal in the

SerialLite II MegaCore.

Required

Enable rate match FIFO

Enables support for rate match FIFO.

Optional

Create optional rate match FIFO

status ports

Enable the status ports for rate match FIFO.

Optional

Enable 8B/10B encoder/decoder

Provide the following ports:

■

rx_runningdisp—provides running disparity status to the

err_rr_disp

signal in the SerialLite II core.

■

rx_datak—indicates whether the rx_parallel_data output port

contains data or control symbol.

Required

Enable manual disparity control

Enables manual disparity control for the 8B/10B encoder/decoder.

Off

Create optional 8B/10B status ports

Provide the following status ports for the 8B/10B encoder/decoder

operation:

■

rx_errdetect

■

rx_disperr

Optional

Enable byte ordering block

Enables byte ordering pattern configuration.

Off

Enable byte ordering block manual

control

Provides manual control for the byte ordering block.

Off

Allow PLL/CDR reconfiguration

Enables support for dynamic reconfiguration of Tx PLL and Rx CDR.

Off

Table 4–3. Custom PHY IP Core Settings (Part 2 of 2)

Option

Description

Setting