External clock modes, Seriallite ii internal clocking configurations – Altera SerialLite II IP Core User Manual

Page 59

Chapter 4: Functional Description

4–5

Clocks and Data Rates

January 2014

Altera Corporation

SerialLite II MegaCore Function

User Guide

■

1,024/1,320 × 3.2 = 2.482 Gbps

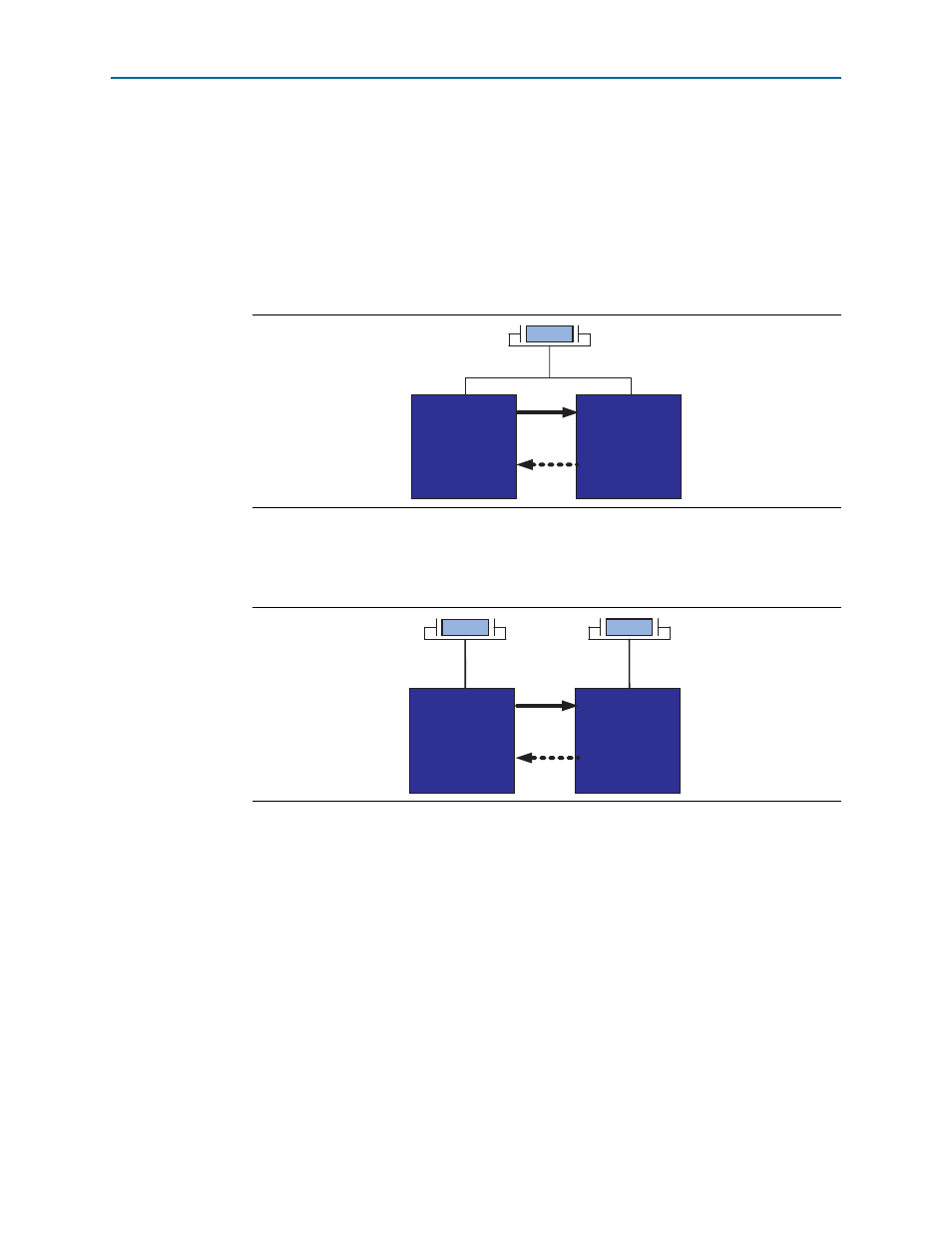

External Clock Modes

You can configure the SerialLite II MegaCore function to use one of two clock modes:

synchronous or asynchronous.

A synchronous configuration is typically used for a link where both ends are on the

same board or on two boards driven by the same system clock (refer to

).

An asynchronous configuration is typically used when the two ends of the link are on

different boards, each having its own independent clock source (refer to

SerialLite II Internal Clocking Configurations

This section contains diagrams illustrating internal clocking configurations.

For Arria V, Cyclone V, and Stratix V configurations, you must identify the PLL

reference clock frequency of the Custom PHY IP core and set the value accordingly in

the .sdc file of the SerialLite II MegaCore function for design integration between both

cores.

Figure 4–4. Synchronous Mode

Figure 4–5. Asynchronous Mode

FPGA 1

FPGA 2

Ref

Clk

CDR

Lanes

FPGA 1

FPGA 2

Ref

Clk1

CDR

Lanes

Ref

Clk2