Pin_mon tasks - verilog hdl, Clock and reset generator, Custom phy ip core – Altera SerialLite II IP Core User Manual

Page 102: Example testbench – verilog hdl, Pin_mon tasks - verilog hdl –16, Example testbench – verilog hdl –16

5–16

Chapter 5: Testbench

Example Testbench – Verilog HDL

SerialLite II MegaCore Function

January 2014

Altera Corporation

User Guide

Pin_mon Tasks - Verilog HDL

shows the function of the pin_mon tasks.

Clock and Reset Generator

The DUT and the SISTER use a common clock, with the frequency set by the

MegaWizard Plug-In Manager.

There is one master reset signal (reset_n) that resets all the logic in the demonstration

testbench (DUT, SISTER(s), AGENs, AMONs and status monitors).

1

Ensure reset_n to the MegaCore function starts high at Time=0, and then goes low for

proper reset of the simulation model. Some simulators do not detect the transition if

reset_n

is asserted low at T=0.

To allow for easy modification, the reset section of the testbench is marked by

start–end comment tags:

SERIALLITE2_TB_RESET_START

SERIALLITE2_TB_RESET_END

1

The clock and reset utilities are included in the testbench top-level file.

Custom PHY IP Core

The DUT and the SISTER use an external transceiver for Arria V and Stratix V

configurations. You are required to separately instantiate the Custom PHY IP core

using the MegaWizard Plug-In Manager.

Example Testbench – Verilog HDL

To allow for easy modification of the demonstration testbench, its main section is

marked by start–end tags:

//SERIALLITE2_TB_MAIN_START

//SERIALLITE2_TB_MAIN_END

Because there is no Atlantic to Atlantic score-boarding, the demonstration testbench

focuses on passing error-free data rather than errored data. Any error condition that

involves dropped or errored packets, must be handled in the testbench by setting

proper expectations.

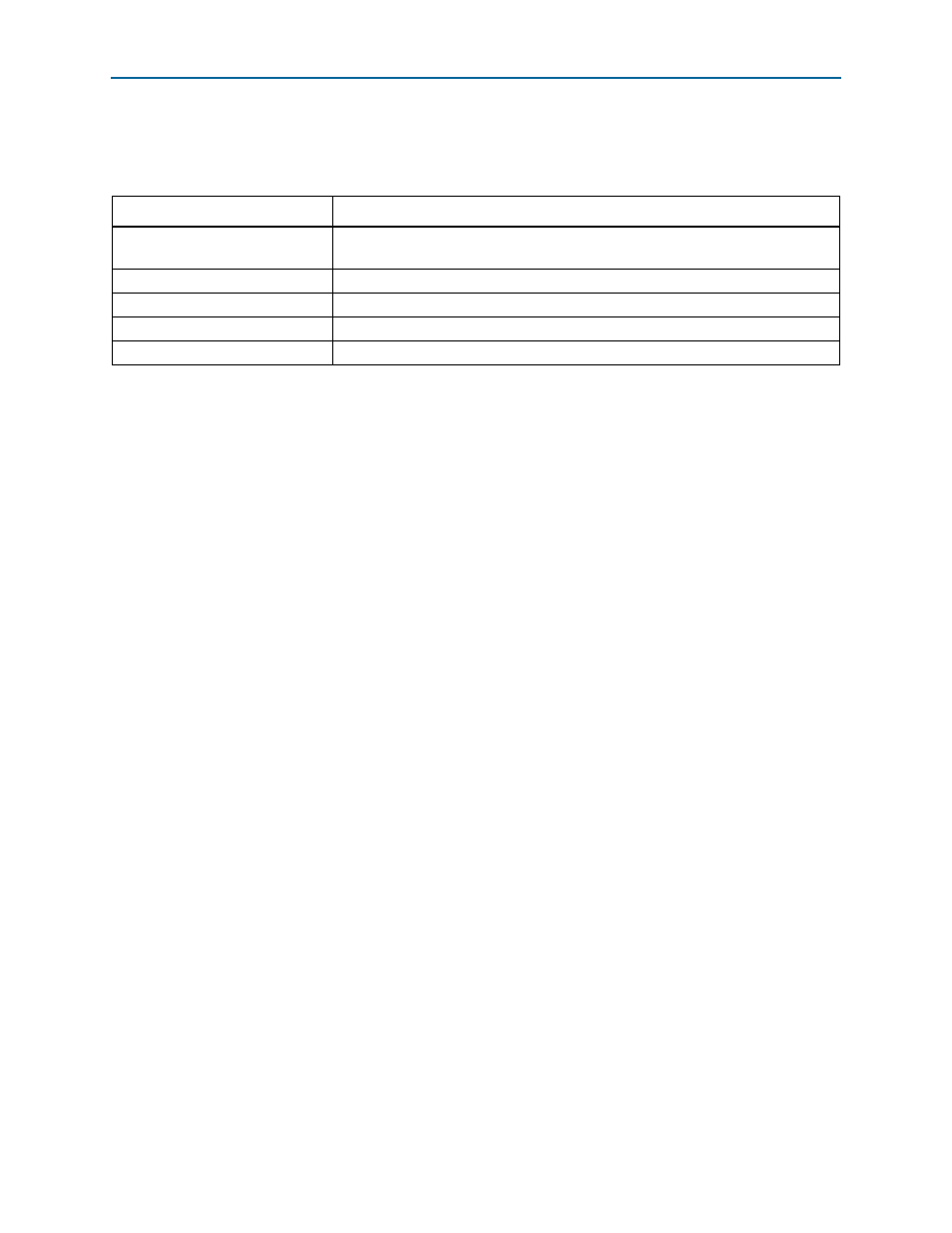

Table 5–11. pin_mon Tasks

Task

Function

on

This task enables monitoring (the en input pin must also be set high to enable

monitoring).

off

This task disables monitoring (regardless of the value of the en input pin).

verbose_on

This task enables the display of verbose messages.

verbose_off

This task disables the display of verbose messages.

set_expect (bit_value)

This task sets the expected pin value.