Testbench, Simulation support, Testbench –20 simulation support –20 – Altera SerialLite II IP Core User Manual

Page 74

4–20

Chapter 4: Functional Description

MegaCore Configuration for Arria V, Cyclone V, and Stratix V Devices

SerialLite II MegaCore Function

January 2014

Altera Corporation

User Guide

Testbench

For the SISTER MegaCore function instance, you are required to edit the SerialLite II

MegaCore function dynamically generated testbench to include the Custom PHY IP

core instantiation. The testbench verifies whether the integration of both cores is

functionally correct in the simulation.

f

The SISTER MegaCore function is a SerialLite II MegaCore function with parameters

derived from the DUT parameters. For more information about the testbench, refer to

“Testbench Specifications” on page 5–2

Simulation Support

The Quartus II software generates the simgen netlist, which contains only the

SerialLite II MegaCore function soft logic. The hard transceiver instantiation logic is

not included. You are required to add the Custom PHY IP core simulation files into

the command line Tcl file (<top level design name>_run_modelsim.tcl) to enable the

simulation to work in the Modelsim simulator.

f

For more information about the compilation and simulation flow, refer to the design

example for

Parameter Settings For SerialLite II MegaCore and Custom PHY IP Core

The parameters associated with the transceiver configuration (Configure Transceiver

page) in the SerialLite II MegaCore function are disabled since there is no hard

transceiver in this configuration. Other parameters for the SerialLite II MegaCore

function remains the same and are enabled. Refer to

“Parameter Settings” on page 3–1

for a more detailed description of the parameters.

The SerialLite II MegaCore function requires specific features to be enabled on the

Custom PHY IP core to support this configuration.

Table 4–3

list the options that you

can set using the Custom PHY IP core parameter editor in the MegaWizard Plug-In

Manager. Note that the required ports are essential for the Custom PHY IP core

instantiation.

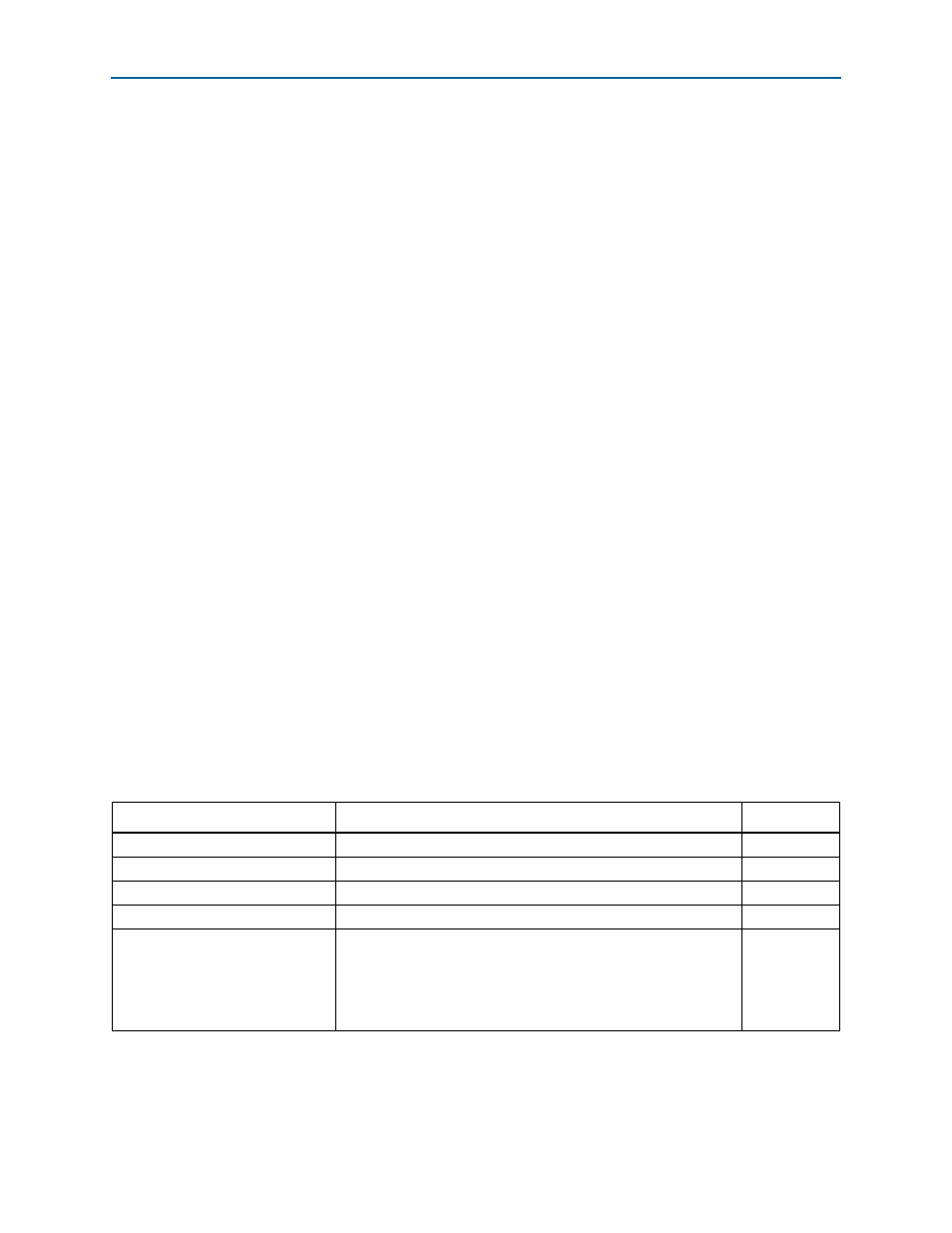

Table 4–3. Custom PHY IP Core Settings (Part 1 of 2)

Option

Description

Setting

pll_locked output port

Provides Tx PLL locking status in the Custom PHY IP core.

Optional

tx_ready output port

Indicates that the Custom PHY IP core is ready to transmit data.

Required

rx_ready output port

Indicates that the Custom PHY IP core is ready to receive data.

Required

Enable TX Bitslip

Provides control for bitslip functionality.

Off

Create rx_coreclkin port

Provides transceiver clock output to the rx_coreclk signal in the

SerialLite II MegaCore.

For Arria V, Cyclone V, and Stratix V designs with more than 1

channel, connect transceiver PHY rx_clkout(0) to

rx_coreclkin (N-1:0)

.

Required