Initialization and restart, Initialization and restart –17, Transmitter link layer – Altera SerialLite II IP Core User Manual

Page 71

Chapter 4: Functional Description

4–17

Clocks and Data Rates

January 2014

Altera Corporation

SerialLite II MegaCore Function

User Guide

Initialization and Restart

Before the SerialLite II link can operate, the MegaCore function must properly reset

the GX transceiver. The SerialLite II MegaCore function must then be initialized and

trained. The SerialLite II training sequence can generally bring the link up in a few

hundred microseconds; the actual amount of time required varies according to PLL

lock times, the number of lanes, the per-lane deskew, and other variation-specific

factors. The reset of the GX transceiver is controlled by the mreset_n and

gxb_powerdown

signals. The minimum pulse width is determined by characterization.

Currently, a 2 ms pulse width is sufficient for the gxb_powerdown input, and three

cycles for the mreset_n signal. For simulation, a reset duration of several clock cycles

(for example, 10) is sufficient.

A link only restarts on its own if a link error occurs during normal operation. A

hardware reset using the mreset_n signal also brings down the link when the reset is

asserted low and reestablishes the link when the reset is released. When one end of

the link is brought down by either of these means, it brings the other end down by

sending training sequences to the other end of the link. The other end of the link

restarts after it sees eight successive training sequences.

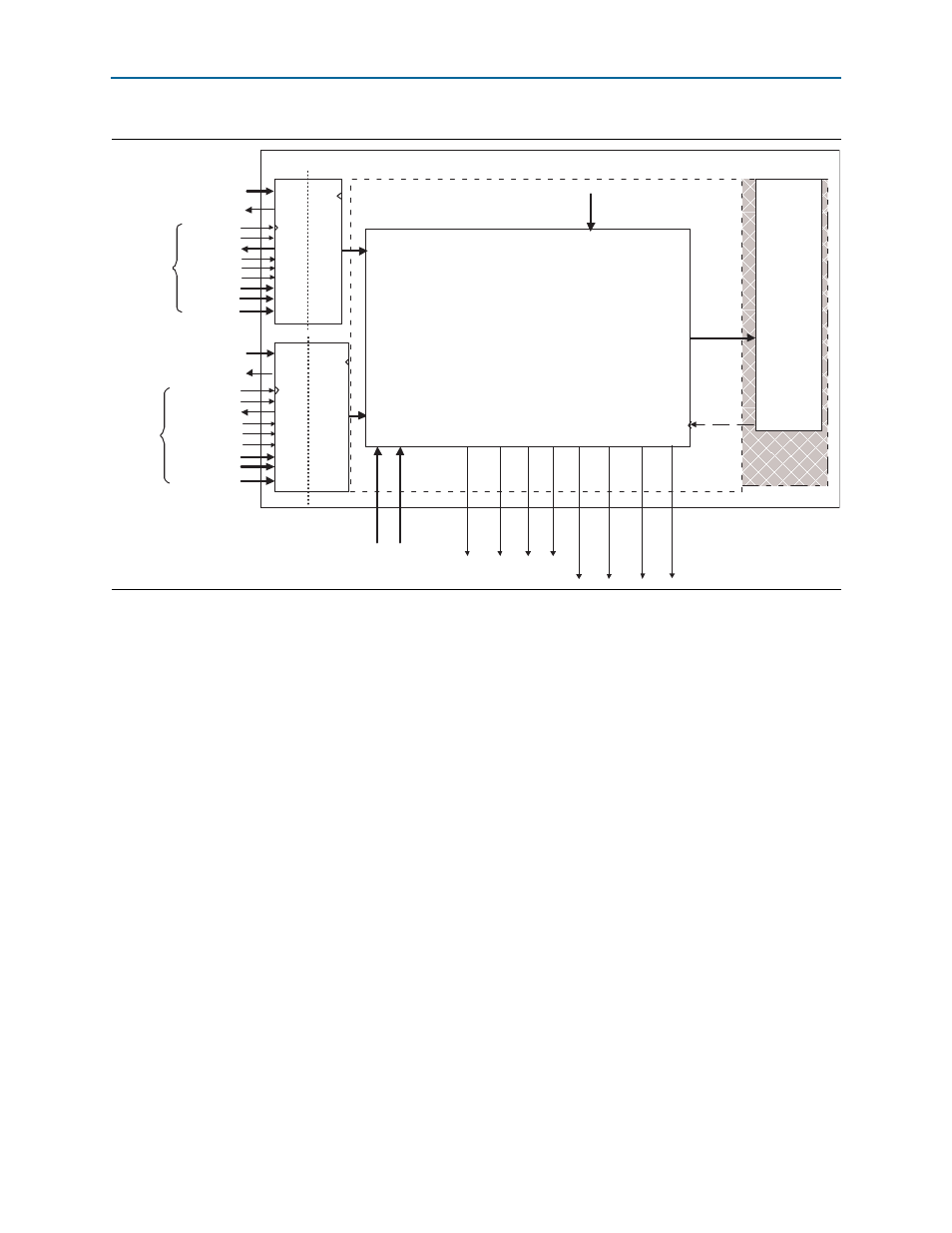

Figure 4–16. Transmitter Link Layer

slite2_top

high speed

front end (Phy)

slite2_ll

TX Core

Phy Layer

Blocks

(Ex xcvr,

slite2_phy)

ctr

l_tc_r

dp_fctime

Regular Data

Port Atlantic

FIFO

(txrdp_atltop

)

txrdp_ena

txrdp_dav

txrdp_sop

txrdp_eop

txrdp_err

txrdp_mty

txrdp_dat

txrdp_adr

txrdp_clk

ctl_txrdp_fth

Atlantic

Interface

(Reg Data

Packets )

High Priority

Port Atlantic

FIFO

(txhpp_atltop)

err_txhpp_oflw

ctl_txhpp_fth

tx_coreclock

txhpp_ena

txhpp_dav

txhpp_sop

txhpp_eop

txhpp_err

txhpp_mty

txhpp_dat

txhpp_adr

txhpp_clk

Atlantic

Interface

(Priority

Packets )

ctr

l_tc_hpp_fctime

err_txrdp_oflw

err_tc_roe_rsnd_gt4

stat_tc_roe_timeout

err_tc_is_drop

err_tc_lm_fif

o_ofl

w

stat_tc_fc_rdp_retr

ansmit

stat_tc_fc_hpp_retr

ansmit

stat_tc_rdp_thresh_breach

stat_tc_hpp_thresh_breach

rx2tx_retimer_fifo