Fifo buffer size, Fifo buffer structure, Fifo buffer size –20 fifo buffer structure –21 – Altera SerialLite II IP Core User Manual

Page 44

Chapter 3: Parameter Settings

3–21

Link Layer Configuration

January 2014

Altera Corporation

SerialLite II MegaCore Function

User Guide

FIFO Buffer Size

The size of the FIFO buffers is based on the factors listed in

.

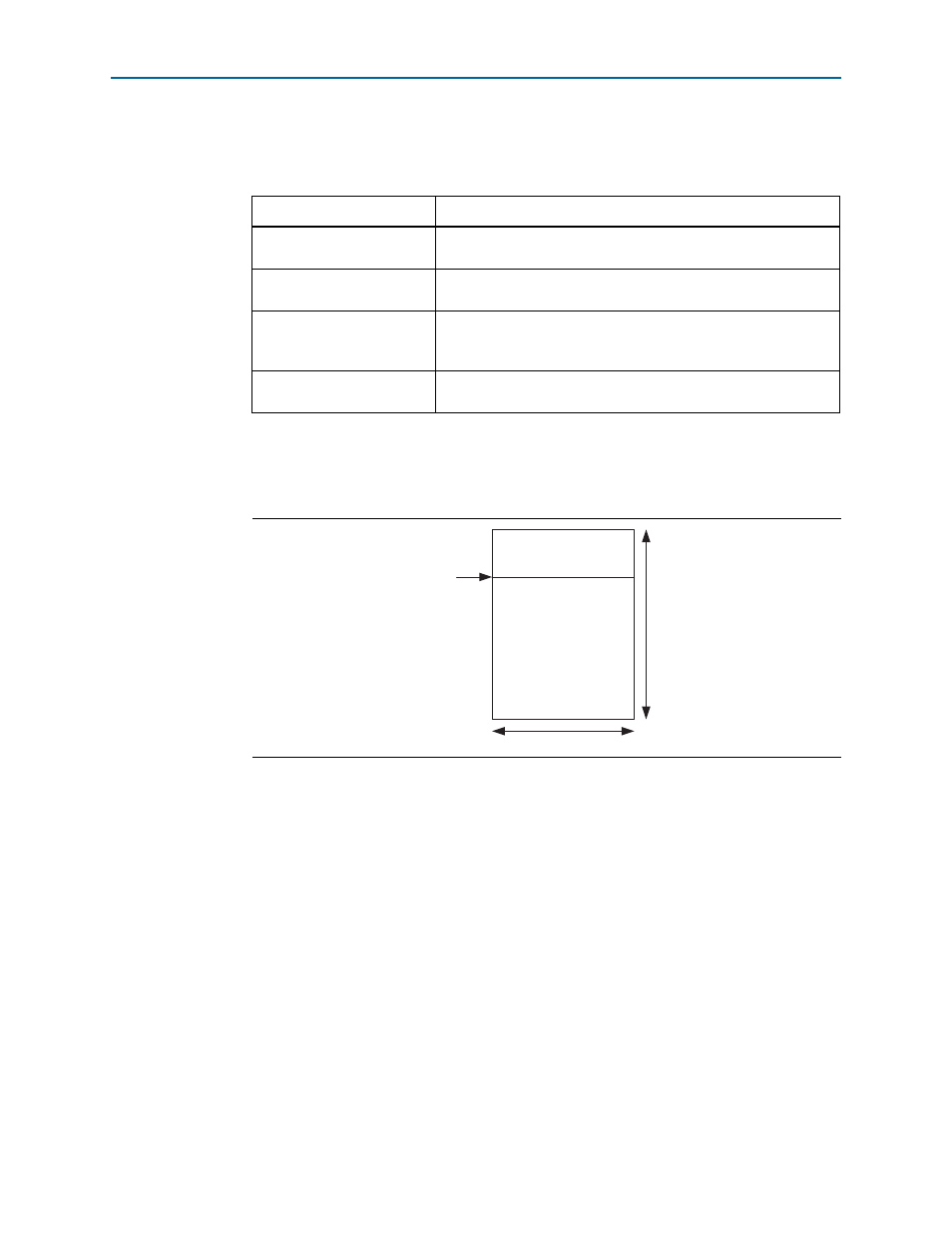

FIFO Buffer Structure

shows the Atlantic FIFO buffer structure.

The FIFO buffer threshold low (FTL), ctl_rxrdp_ftl/ctl_rxhpp_ftl, value for

receiver variations controls when the rxrdp_dav/rxhpp_dav signals are asserted for

the read side of the FIFO buffer, respectively. If the fill level of the buffer is higher than

the FTL value, the rxrdp_dav/rxhpp_dav signal is asserted indicating that there is a

burst of data available.

1

There is no requirement to wait for the rxrdp_dav/rxhpp_dav signal to be asserted;

you can read from the buffer at any time by asserting the rxrdp_ena/rxhpp_ena signal

at all times and qualifying the data with the rxrdp_val/rxhpp_val signal. The FIFO

buffer has built-in underflow protection, such that an underflow condition does not

exit.

Table 3–7. Factors Affecting Receive FIFO Buffer Size

Factor

Description

Flow control

If flow control is enabled, the FIFO buffer size should change to

account for the thresholds that must be set.

Pause duration

When optimizing against starvation during flow control, the pause

duration affects the FIFO buffer size.

Number of packets (and

packet sizes)

If you want to use a store-and-forward FIFO (using the eop_dav

and a high threshold), the FIFO must be big enough to hold a full

packet at minimum.

Wire delay and bit rate

The wire propagation delay and the bit rate change the wire latency,

which must be accommodated if flow control is used.

Figure 3–13. Atlantic FIFO Buffer Structure

Width set automatically

Threshold

Headroom

FTL/FTH

Total

depth