Altera SerialLite II IP Core User Manual

Page 79

Chapter 4: Functional Description

4–25

Signals

January 2014

Altera Corporation

SerialLite II MegaCore Function

User Guide

shows the Atlantic interface signals.

f

For more information on this interface, refer to the

.

1

These signals are only present when the Link Layer mode is enabled and the Atlantic

FIFO buffer is used.

1

There are no specific requirements for Atlantic clocks (rxrdp_clk, rxhpp_clk,

txrdp_clk

and txhpp_clk) as they are all system dependent. The Atlantic clocks at the

read side must be fast enough to prevent backpressure which decreases bandwidth

efficiency.

gxb_powerdown

Input

—

Transceiver block reset and power down. This

signal resets and powers down all circuits in the

transceiver block. This does not affect the refclk

buffers and reference clock lines. All the

gxb_powerdown

input signals of cores placed in

the same transceiver block should be tied

together.The gxb_powerdown signal should be tied

low or should remain asserted for at least 2ms

whenever it is asserted.

Notes to

(1) rxnl is the receive number of lanes; txnl is the transmit number of lanes.

(2) srx is the transfer size × the receive number of lanes.

(3) recon_quad is the total number of Quads being used.

(4) If the altgx_reconfig block is not used, the signal will not toggle (set to a fixed value) and thus is not on any clock domain. If the

altgx_reconfig

block is used, this signal is on the reconfig_clk domain.

(5) This signal is removed in configurations targeted for Arria V and Stratix V devices due to the exclusion of hard transceivers.

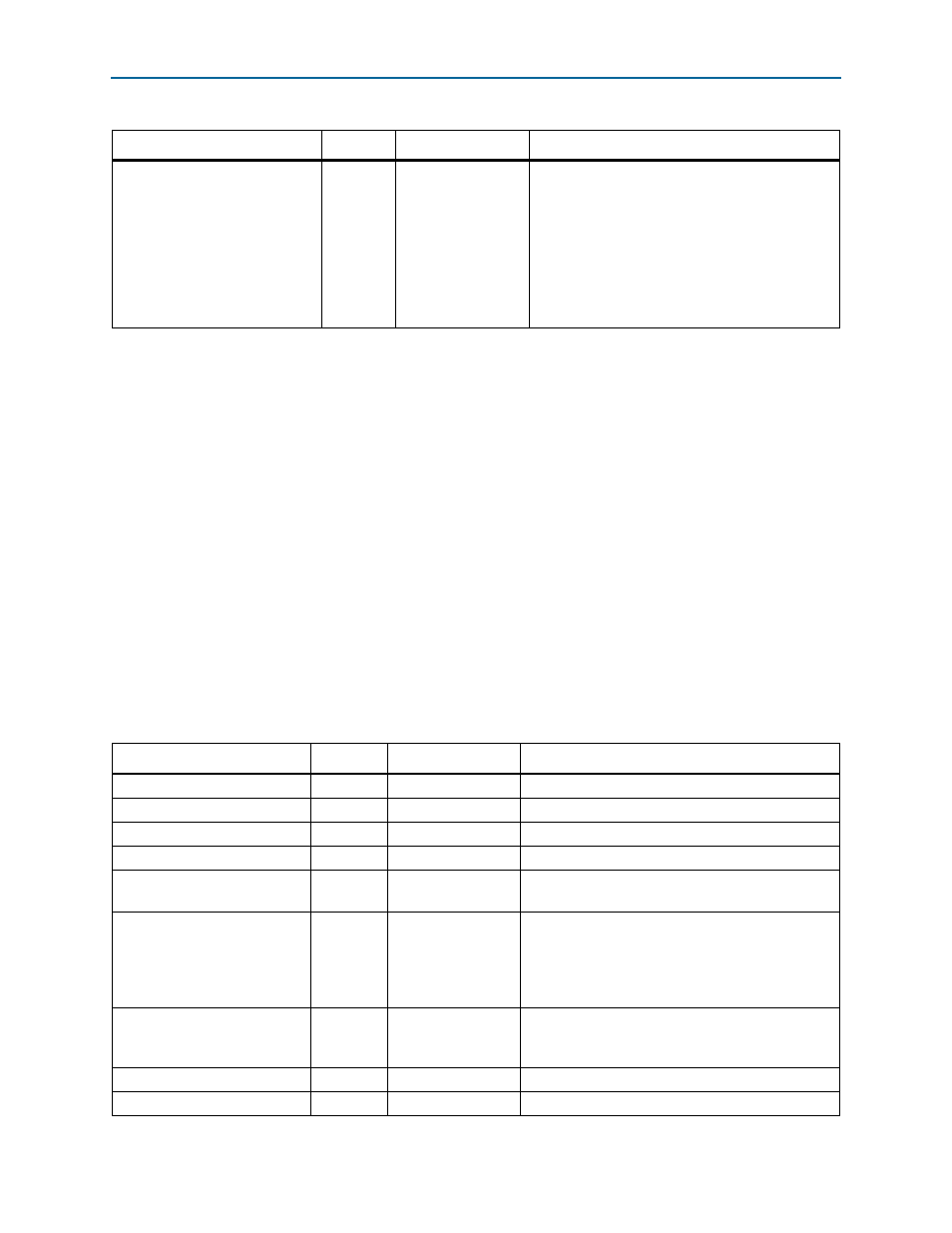

Table 4–6. Transceiver Megafunction Signals (Part 3 of 3)

Signal

(1)

,

(2)

Direction

Clock Domain

Description

Table 4–7. Atlantic Interface Signals (Part 1 of 3)

Signal

Direction

Clock Domain

Description

rxrdp_clk

Input

—

Atlantic receive regular data port clock.

txrdp_clk

Input

—

Atlantic transmit regular data port clock.

rxhpp_clk

Input

—

Atlantic receive high priority port clock.

txhpp_clk

Input

—

Atlantic transmit high priority port clock.

rxrdp_ena

Input

rxrdp_clk

Enable signal on the Atlantic interface. Indicates that

the data is to be read on the next clock cycle.

rxrdp_dav

Input

rxrdp_clk

Input (No FIFO buffer) determines whether flow

control is required on this port. When this signal is

low, the fill level has been breached. When this signal

is high, the FIFO buffer has enough space for more

words.

rxrdp_dav

Output

rxrdp_clk

Output (With FIFO buffer) represents the buffer’s fill

level. This signal is high when the level is above FTL

or if an EOP is in the buffer.

rxrdp_val

Output

rxrdp_clk

The output data is valid.

rxrdp_sop

Output

rxrdp_clk

Start of packet indicator on the Atlantic interface.