Figure 3–5, Refer to, Figure 3–6 – Altera SerialLite II IP Core User Manual

Page 29

Advertising

3–6

Chapter 3: Parameter Settings

Physical Layer Configuration

SerialLite II MegaCore Function

January 2014

Altera Corporation

User Guide

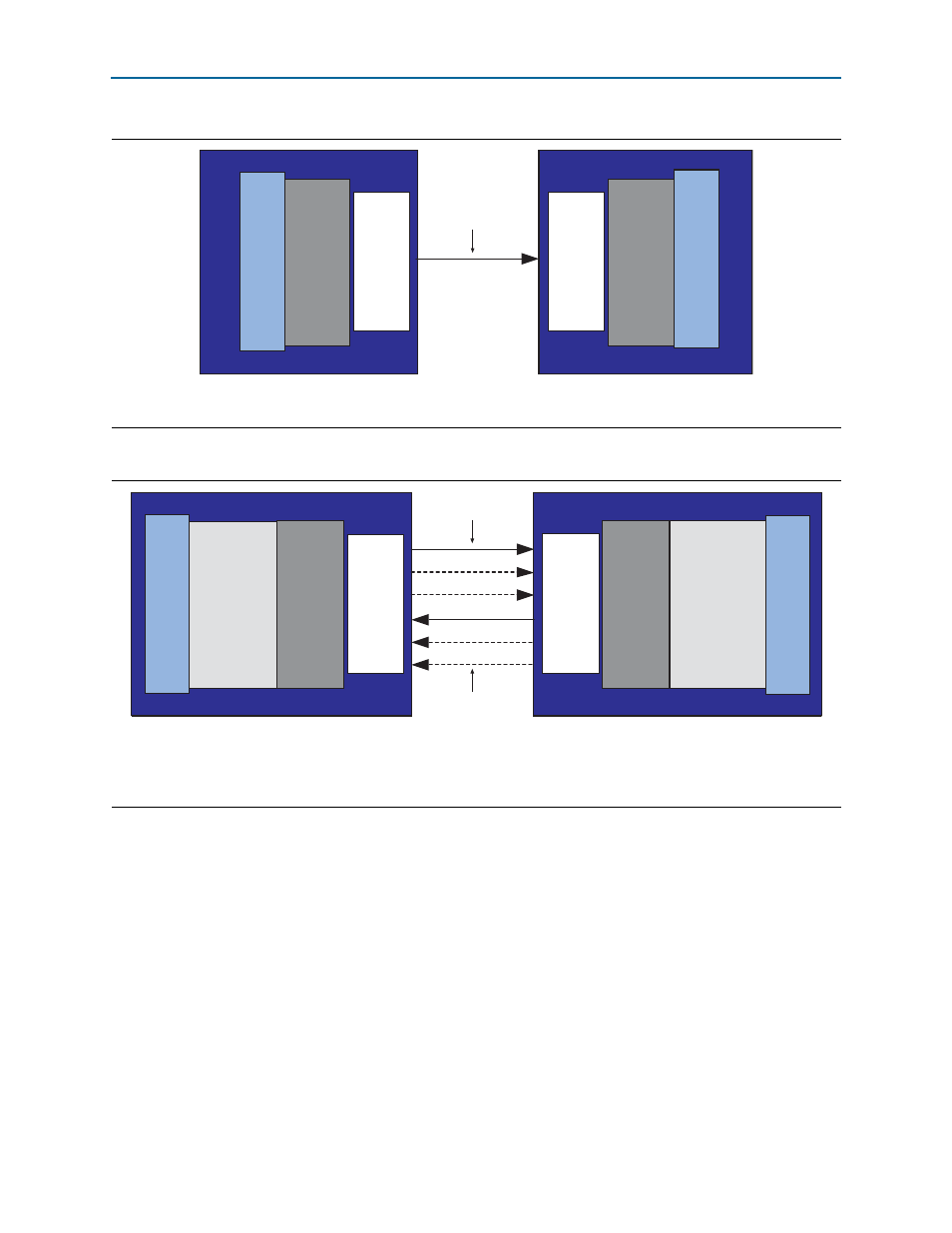

Figure 3–5. Streaming Simplex Mode Block Diagram

Note to

(1) A full line indicates a mandatory lane

One lane only

FPGA 1

PHY

Layer

FPGA 2

PHY

Layer

Atlantic

Interface

CDR

SERDES

CDR

SERDES

Atlantic

Interface

Figure 3–6. Asymmetric Mode Block Diagram

Notes to

(1) A full line indicates a mandatory lane.

(2) A dashed line indicates an optional lane.

One or more lanes

(up to N)

FPGA 1

Light-weight

Linklayer

PHY

Layer

FPGA 2

Light-weight

Linklayer

PHY

Layer

Atlantic

Interface

CDR

SERDES

CDR

SERDES

One or more lanes

(up to M, but

not equal to N)

Atlantic

Interface

Advertising