General description, General description –3 – Altera SerialLite II IP Core User Manual

Page 8

Chapter 1: About This MegaCore Function

1–3

General Description

January 2014

Altera Corporation

SerialLite II MegaCore Function

User Guide

■

IP functional simulation models for use in Altera-supported VHDL and Verilog

HDL simulators

■

Support for OpenCore

®

Plus evaluation

General Description

The SerialLite II MegaCore function is a simple, high-speed, low-latency, and

low-resource point-to-point serial data communication link.

The MegaCore function performs up to the following rates:

■

3.75 Gbps in Arria II GX devices

■

5 Gbps in Cyclone V devices

■

6.375 Gbps in Stratix IV, Arria V, and Stratix V devices

The SerialLite II MegaCore function is highly configurable, and provides a wide range

of functionality suited to moving data in many different environments.

The SerialLite II MegaCore function provides a simple and lightweight way to move

data from one point to another reliably at high speeds. It consists of a serial link of up

to 16 bonded lanes, with logic to provide a number of basic and optional link support

functions. The Atlantic interface is the primary access for delivering and receiving

data.

The SerialLite II protocol specifies a link that is simple to build, uses as little logic as

possible, and requires little work for a logic designer to implement. The SerialLite II

MegaCore function uses all of the features available in the SerialLite II protocol. You

can parameterize the MegaCore function using the SerialLite II parameter editor.

A link built using the SerialLite II MegaCore function operates at 622 Mbps to 6.375

Gbps per lane. Link reliability is enhanced by the 8B10B encoding scheme and

optional CRC capabilities. You can achieve further reductions in the bit-error rate by

using the optional retry-on-error feature. Data rate and consumption mismatches can

be accommodated using the optional flow-control feature to ensure that no data is

lost.

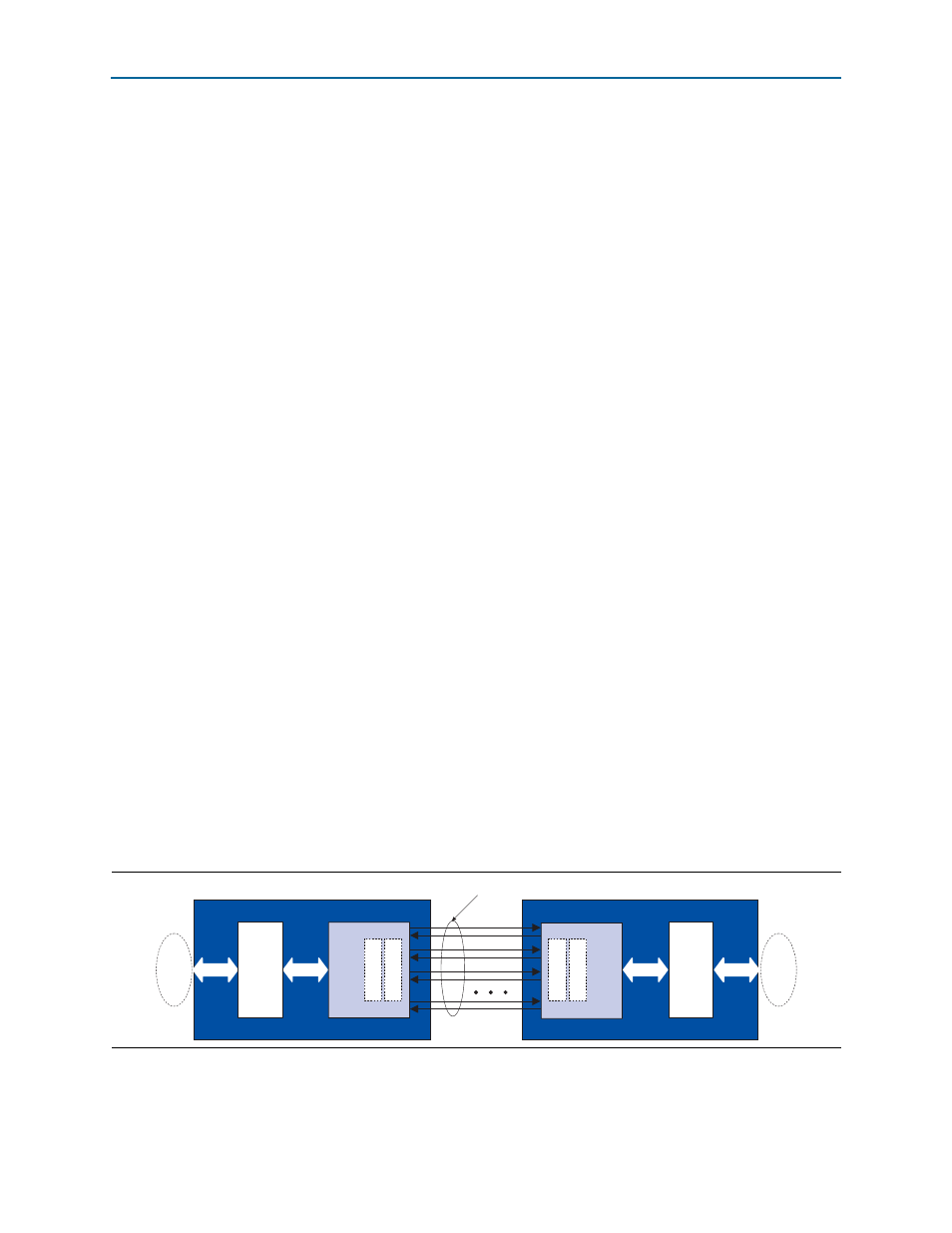

shows that the SerialLite II MegaCore function is divided into two main

blocks: a protocol processing portion (data link layer) and a high-speed front end

(physical layer).

You can use the SerialLite II MegaCore function in the following applications:

■

Chip-to-chip connectivity

Figure 1–1. SerialLite II MegaCore Function High-Level Block Diagram

One or More

Lanes

Logical

Electrical

Physical Layer

Link Layer

Logical

Electrical

Physical Layer

Link Layer

User

Application

User

Application