Altera SerialLite II IP Core User Manual

Page 78

4–24

Chapter 4: Functional Description

Signals

SerialLite II MegaCore Function

January 2014

Altera Corporation

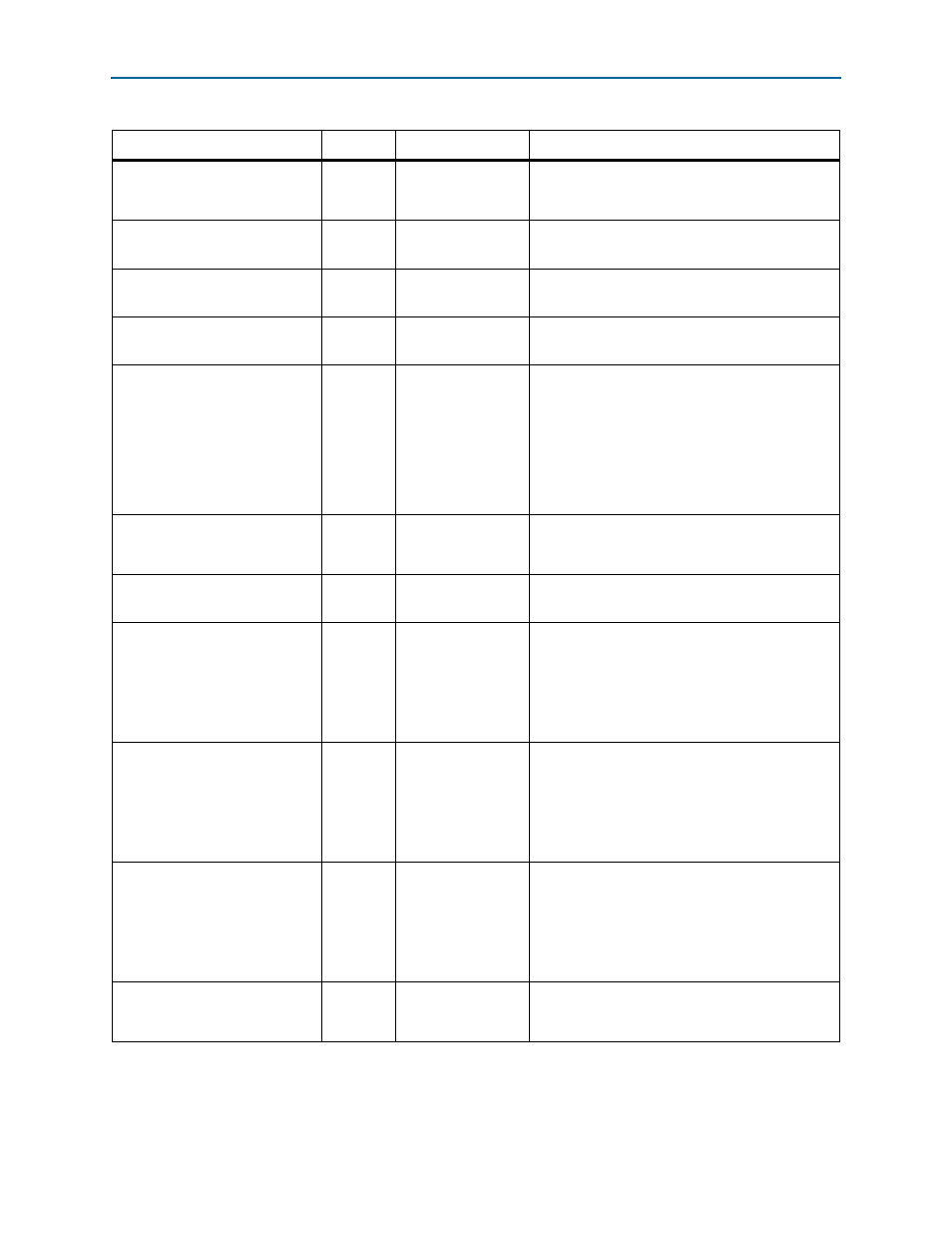

User Guide

err_tc_pcfifo_uflw

[txnl-1:0]

Output

tx_coreclock

Interface/phase compensation FIFO buffer

underflow signal (Arria II GX and Stratix IV devices

only).

err_tc_pcfifo_oflw

[txnl-1:0]

Output

tx_coreclock

Interface/phase compensation FIFO buffer overflow

signal (Arria II GX and Stratix IV devices only).

stat_rr_sigdet

[rxnl-1:0]

Output

rrefclk

This signal is for debugging purposes only and can

be ignored.

stat_rr_gxsync

[srx-1:0]

Output

rrefclk

Gives the status of the pattern detector and word

aligner.

stat_rr_rxlocked

[rxnl-1:0]

Output

rrefclk

Receiver PLL locked signal. Indicates whether or

not the receiver PLL is phase locked to the CRU

reference clock. When the PLL locks to data, which

happens some time after the transceiver’s

rx_freqlocked

signal is asserted high, this signal

has little meaning because it only indicates lock to

the reference clock. This signal is active high for

Arria II GX and Stratix IV devices.

stat_rr_freqlock

[rxnl-1:0]

Output

rrefclk

Frequency locked signal from the CRU. Indicates

whether the transceiver block receiver channel is

locked to the data mode in the rxin port.

stat_rr_pattdet

[srx-1:0]

Output

rrefclk

Pattern detection signal

reconfig_fromgxb

,

Arria II GX or Stratix IV GX:

[recon_quad*17-1:0]

Output

reconfig_clk

ALTGX Reconfig from the GXB Bus.

This signal is connected to the reconfig_fromgxb

port on the altgx_reconfig module. If you use

Arria II GX or Stratix IV device, you must connect

this output to the altgx_reconfig module for

offset cancelation.

reconfig_togxb

Arria II GX or Stratix IV GX:

[3:0]

Input

reconfig_clk

ALTGX Reconfig to the GXB Bus.

This signal is connected to the reconfig_togxb

port on the altgx_reconfig module. If you use

Arria II GX or Stratix IV device, you must connect

this output to the altgx_reconfig module for

offset cancelation.

reconfig_clk

Input

—

ALTGX Reconfig Clock to the GXB.

This signal is connected to the reconfig_clk port

on the altgx_reconfig module. If you use

Arria II GX or Stratix IV device, you must connect

this output to the altgx_reconfig module for

offset cancelation.

cal_blk_clk

Input

—

Calibration clock for the termination resistor

calibration block. The frequency range of

cal_blk_clk

is 10 to 125 MHz.

Table 4–6. Transceiver Megafunction Signals (Part 2 of 3)

Signal

(1)

,

(2)

Direction

Clock Domain

Description