Multiple core configuration, Multiple core configuration –18 – Altera SerialLite II IP Core User Manual

Page 72

4–18

Chapter 4: Functional Description

Multiple Core Configuration

SerialLite II MegaCore Function

January 2014

Altera Corporation

User Guide

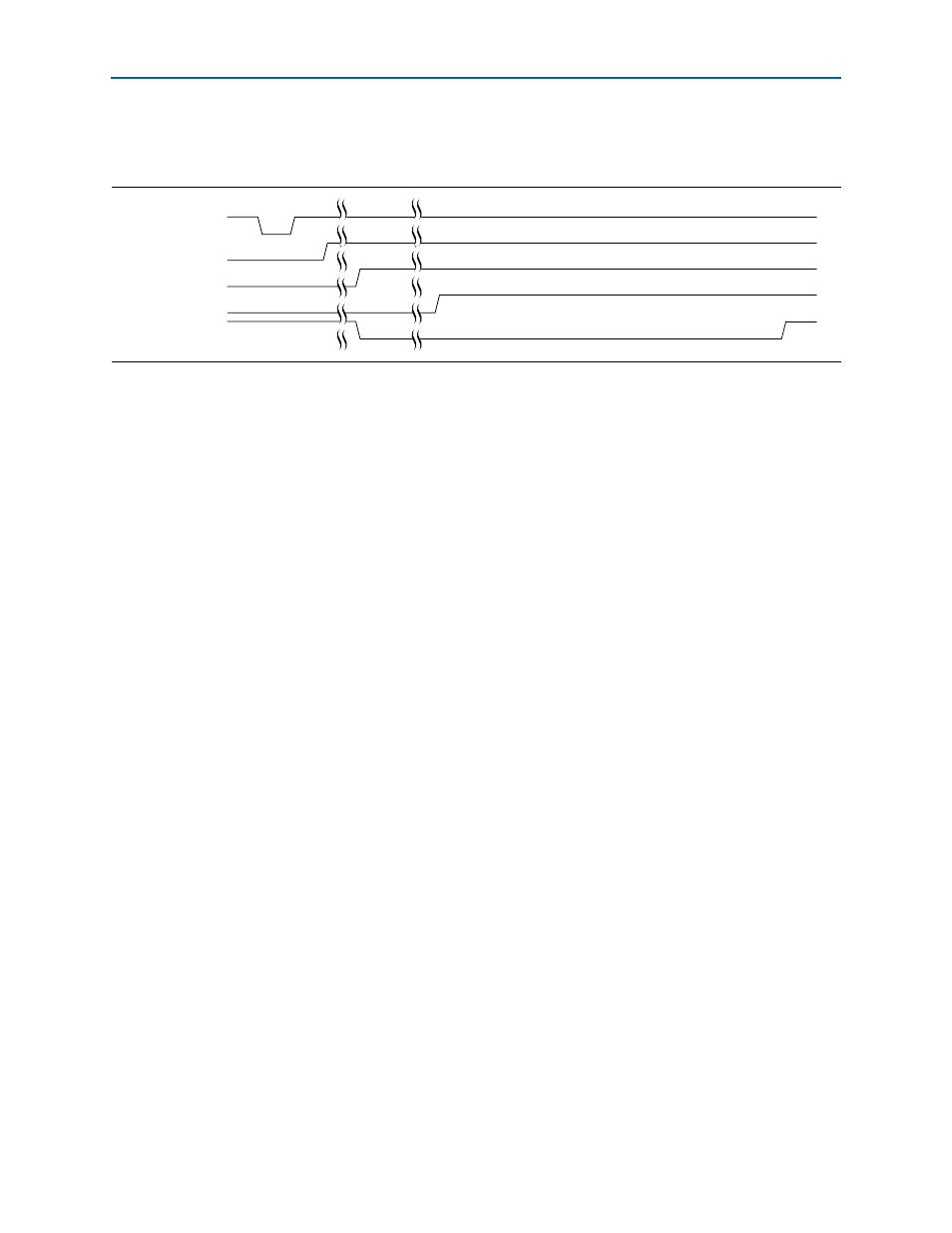

shows what happens when the SerialLite II MegaCore function is

initialized.

When the reset_n input signal is asserted, the transceiver and the MegaCore function

start to reset and initialize the MegaCore function. When the corresponding signals,

stat_tc_pll_locked

, stat_rr_freqlock, and the stat_tc_rst_done signal go high, a

set of training sequence are transmitted across the link to align the characters and

lanes. When everything is synchronized, the link is established and ready to be used,

stat_rr_link

= 1.

Multiple Core Configuration

When you instantiate multiple SerialLite II MegaCore functions, you must apply the

following additional guidelines to create a working design.

■

If you use the Tcl constraints to make assignments for the MegaCore functions,

you must edit the Tcl script associated with each generated SerialLite II MegaCore

function to update the hierarchal paths to each clock node and signal inside the

TCL scripts. You can use the generated scripts as a guide. You must also make

these changes to the generated Synopsys Design Constraints File (.sdc) if you

intend to use the TimeQuest Timing Analyzer.

Note that the Tcl scripts assume a top-level name for several clocks, such as:

trefclk

, rxrdp_clk, rxhpp_clk, txrdp_clk, and txhpp_clk. You must edit Set

Clock Names

in the scripts if the clock name connected to these inputs does not

match. If the multiple cores are connected to the same clocks at the top-level file,

you must make sure Set Clock Names and clock settings are only available in

one script. You must always set to run this script first in the projects. You must edit

the Tcl script and the .sdc file if you plan to use the TimeQuest timing analyzer.

■

For Arria II GX and Stratix IV designs, you must ensure that the cal_blk_clk

input to each SerialLite II MegaCore function is driven by the same calibration

clock source. In addition, ensure that the SerialLite II MegaCore function and other

MegaCore variants in the system that use the ALTGX megafunction have the same

clock source connected to their respective cal_blk_clk ports.

■

In Arria II GX and Stratix IV designs that include multiple SerialLite II cores in a

single transceiver block, the same signal must drive gxb_powerdown to each of the

SerialLite II MegaCore variants.

Figure 4–17. Initialization

mreset_n

stat_tc_pll_locked

stat_rr_freqlock

stat_tc_rst_done

stat_rr_link