Altera SerialLite II IP Core User Manual

Page 77

Chapter 4: Functional Description

4–23

Signals

January 2014

Altera Corporation

SerialLite II MegaCore Function

User Guide

shows the transceiver megafunction signals.

f

For more information on Altera gigabit transceiver (ALTGX)megafunction, refer to

ection in volume 2 of the Arria II GX Device

Handbook, and the

ection in volume 2 of the

Stratix IV Device Handbook.

mreset_n

Input

Asynchronous

Master reset pin, active low. Asserting this signal

causes the entire SerialLite II MegaCore function,

including the Atlantic FIFO buffers, to be reset.

For Arria V, Cyclone V, and Stratix V designs, hold this

signal asserted until the Custom PHY asserts the

tx_ready

and rx_ready output ports.

ctrl_tc_force_train

Input

tx_coreclock

Force training patterns to be sent. Negate once the

receiver has locked. Only used in self-synchronizing

mode. Otherwise, this signal is currently reserved (tie

this signal to 1'b0).

stat_tc_pll_locked

Output

tx_coreclock

PLL locked signal. Indicates that the ALTGX PLL has

locked to the trefclk.

stat_rr_link

Output

rrefclk

Link Status. When high, the link is enabled.

Notes to

(1) n = RX number of lanes

(2) m = TX Number of lanes

(3) In broadcast mode, these signals will have the corresponding receiver function number post-fixed. For example, err_rr_crc0 is the CRC error

signal from SerialLite II receiver block 0.

(4) This signal is removed in configurations targeted for Arria V, Cyclone V, and Stratix V devices due to the exclusion of hard transceivers.

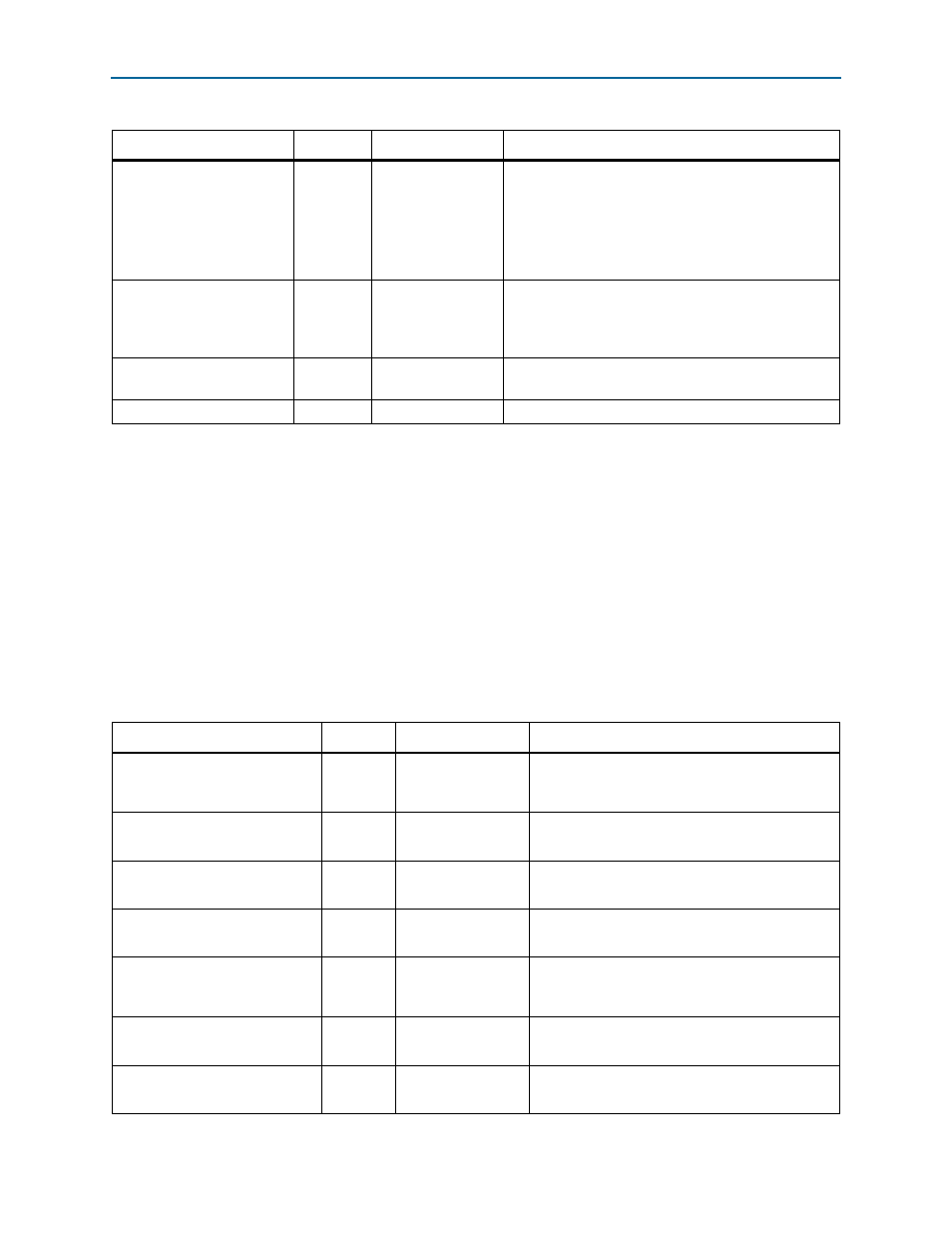

Table 4–5. High-Speed Serial Interface Signals (Part 2 of 2)

Signal

Direction

Clock Domain

Description

Table 4–6. Transceiver Megafunction Signals (Part 1 of 3)

Signal

Direction

Clock Domain

Description

Input

tx_coreclock

Serial Loopback (TXOUT internally connected to

RXIN

). Tie signal to 1'b0 to NOT use loopback, tie

to 1'b1 to Use Serial Loopback.

rcvd_clk_out

[rxnl-1:0]

Output

Per lane recovered clock.

err_rr_8berrdet

[srx-1:0]

Output

rrefclk

8B/10B error detection signal.

err_rr_disp

[srx-1:0]

Output

rrefclk

Disparity error detection signal

err_rr_pcfifo_uflw

[rxnl-1:0]

Output

rrefclk

Interface/phase compensation FIFO buffer

underflow signal (Arria II GX and Stratix IV devices

only).

err_rr_pcfifo_oflw

[rxnl-1:0]

Output

rrefclk

Interface/phase compensation FIFO buffer overflow

signal (Arria II GX and Stratix IV devices only).

err_rr_rlv

[rxnl-1:0]

Output

rrefclk

Run length violation status signal.