Note 1) – Altera External Memory PHY Interface User Manual

Page 27

Chapter 3: Functional Description—ALTMEMPHY (nonAFI)

3–11

ALTMEMPHY Signals

© January 2010

Altera Corporation

External Memory PHY Interface (ALTMEMPHY) (nonAFI) Megafunction User Guide

The ports in

exists for all DDR2/DDR SDRAM variations.

aux_full_rate_clk

output

1

A copy of the mem_clk_2x signal that you can use in

other parts of your design.

Note to

(1) Refer to

for the reset mechanism in Arria GX, Cyclone III, Stratix II and Stratix II GX devices.

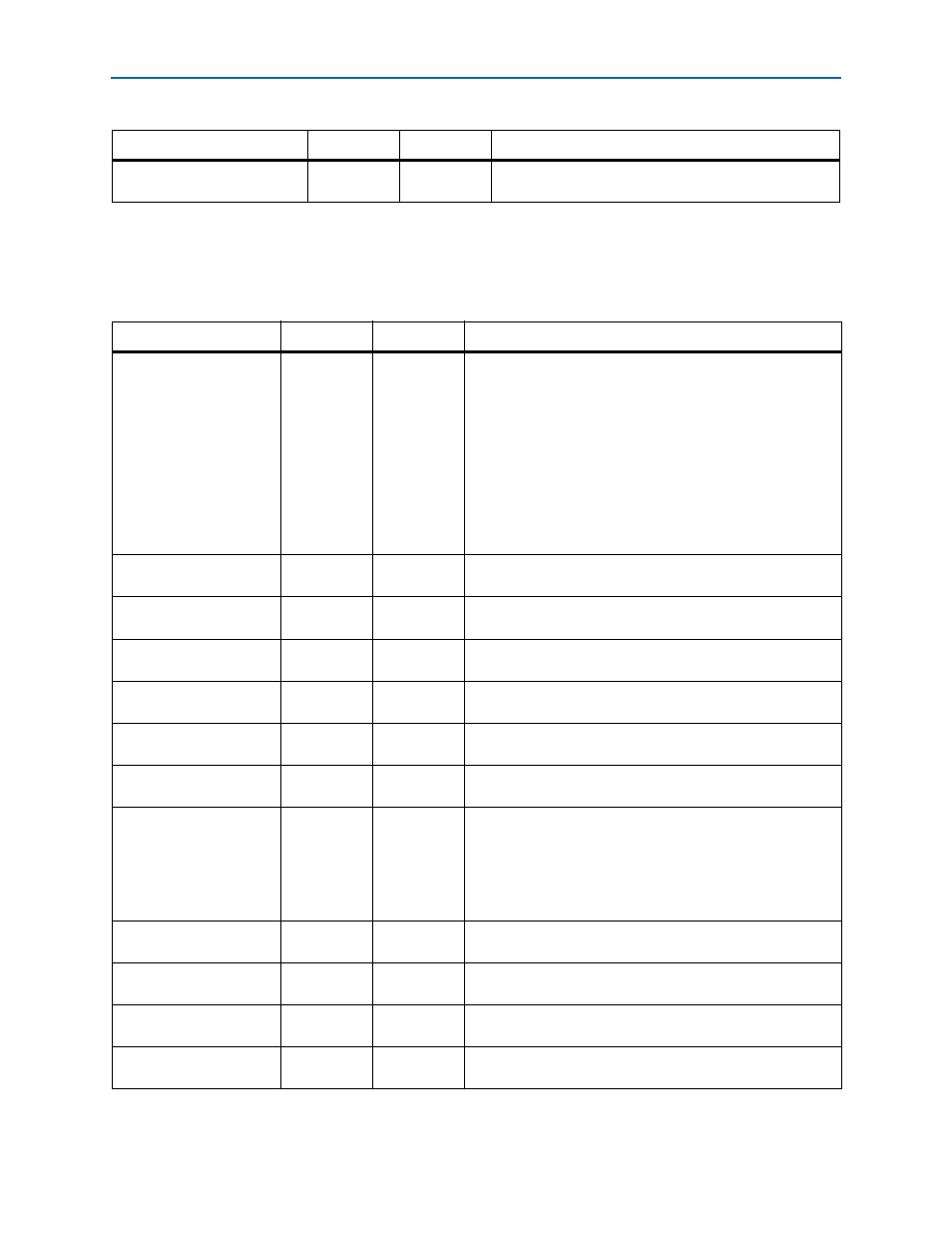

Table 3–2. Clock and Reset Signals for DDR2/DDR SDRAM—nonAFI

(Note 1)

(Part 2 of 2)

Signal Name

Type

Width

Description

Table 3–3. PLL Reconfiguration Signals for DDR2 and DDR SDRAM—nonAFI

Signal Name

Type

Width

Description

pll_reconfig_

enable

input

1

Allows access to the PLL reconfiguration block. Hold this

signal low in normal operation. While the ALTMEMPHY is held

in reset (via the soft_reset_n signal), and the

reset_request_n

signal is 1, it is safe to reconfigure the

PLL. To reconfigure the PLL, set this signal to 1 and use the

other pll_reconfig signals to access the PLL. When

finished reconfiguring, set this signal to 0, and then set the

soft_reset_n

signal to 1 to bring the ALTMEMPHY out of

reset. For this signal to work, the

PLL_RECONFIG_PORTS_EN

parameter must be set to

TRUE

.

pll_reconfig_

write_param

input

1

For more information, refer to the

pll_reconfig_read

_param

input

1

For more information, refer to the

pll_reconfig

input

1

For more information, refer to the

pll_reconfig_

counter_type

input

4

For more information, refer to the

pll_reconfig_

counter_param

input

3

For more information, refer to the

pll_reconfig_data

_in

input

9

For more information, refer to the

pll_reconfig_soft

_reset_en_n

input

1

The asynchronous reset input to the PLL reconfiguration

block. This reset causes a PLL reconfiguration block reset and

holds the reset if the ALTMEMPHY megafunction in reset while

the signal is low. This port only exists in the DDR2/DDR

SDRAM variation for Arria GX, Stratix II, and Stratix II GX

devices.

pll_reconfig_busy

output

1

For more information, refer to the

pll_reconfig_data

_out

output

9

For more information, refer to the

pll_reconfig_clk

output

1

Synchronous clock to use for any logic accessing the PLL

reconfiguration interface.

pll_reconfig_

reset

output

1

Resynchronized reset to use for any logic accessing the PLL

reconfiguration interface.