Altera External Memory PHY Interface User Manual

Page 33

Chapter 3: Functional Description—ALTMEMPHY (nonAFI)

3–17

ALTMEMPHY Signals

© January 2010

Altera Corporation

External Memory PHY Interface (ALTMEMPHY) (nonAFI) Megafunction User Guide

local_powerdn_req

input

1

User control to power down the memory device to

request the controller to place the memory devices

into a power-down state as soon as it can without

violating the relevant timing parameters and

responds by asserting the local_powerdn_ack

signal.

local_self_rfsh_req

input

1

User control of the self-refresh feature to request

that the controller place the memory devices into a

self-refresh state by asserting this signal.

local_self_rfsh_ack

output

1

Self-refresh request acknowledge signal. This signal

is asserted and deasserted in response to the

local_self_rfsh_req

signal from the user.

local_powerdn_ack

output

1

Power-down request acknowledge signal. This

signal is asserted and deasserted in response to the

local_powerdn_req

signal from the user.

Note to

(1) Passed through PHY to the controller.

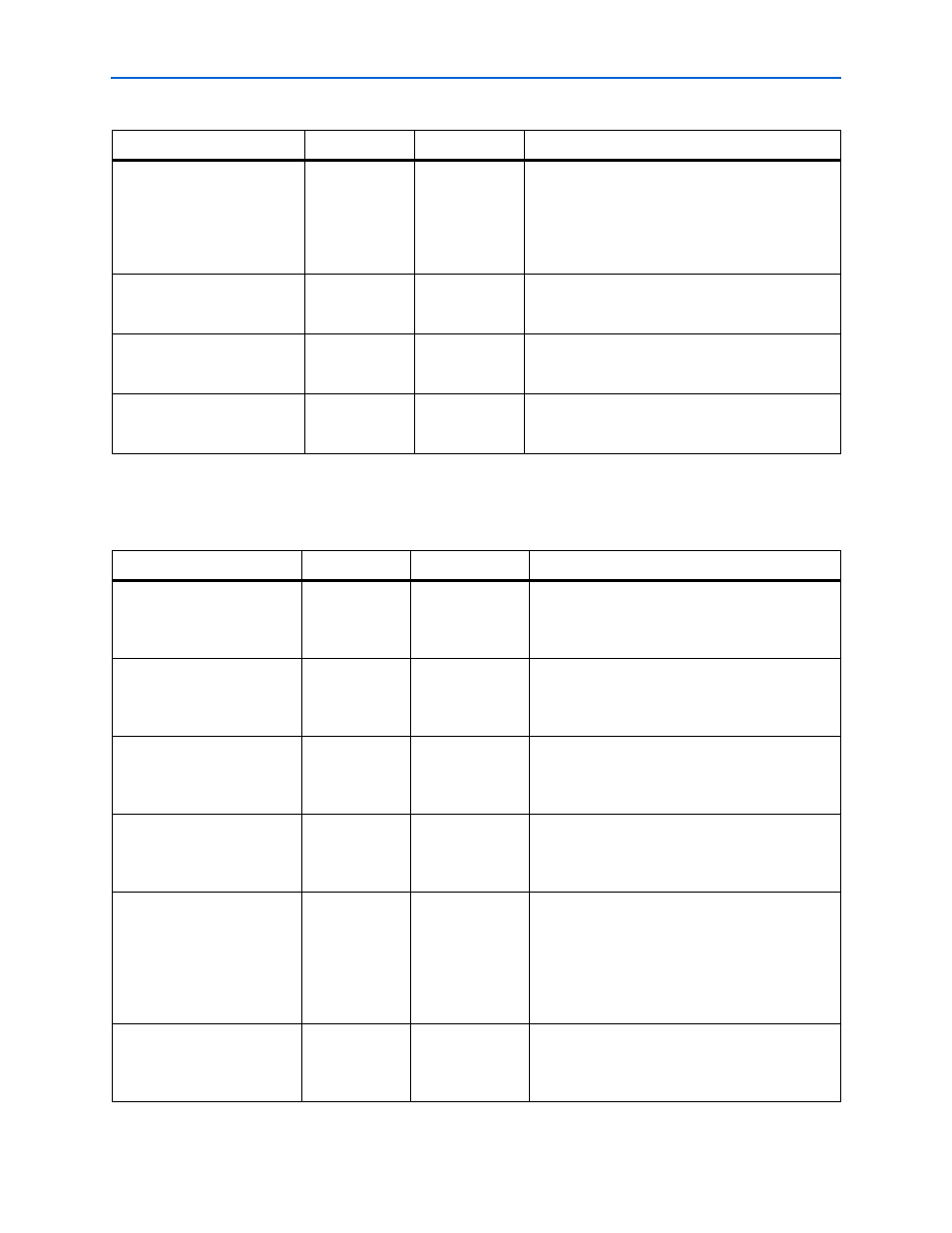

Table 3–7. Local Interface Signals for DDR2 and DDR SDRAM—nonAFI (Part 2 of 2)

(Note 1)

Signal Name

Type

Width

Description

Table 3–8. Datapath Interface for DDR2 and DDR SDRAM—nonAFI (Part 1 of 3)

Signal Name

Type

Width

Description

ctl_mem_addr_h

input

MEM_IF_

ROWADDR_

WIDTH

The row or column address that is sent to the

external memory. Output during the high half-

period of the address and command clock and

driven by the memory controller.

ctl_mem_addr_l

input

MEM_IF_

ROWADDR_

WIDTH

The row or column address that is sent to the

external memory. Output during the low half-period

of the address and command clock and driven by

the memory controller.

ctl_mem_ba_h

input

MEM_IF_

BANKADDR_

WIDTH

The bank address that is sent to the external

memory. Output during the high half-period of the

address and command clock and driven by the

memory controller.

ctl_mem_ba_l

input

MEM_IF_

BANKADDR_

WIDTH

The bank address that is sent to the external

memory. Output during the low half-period of the

address and command clock and driven by the

memory controller.

ctl_mem_be

input

LOCAL_IF_

DWIDTH/8

The optional byte-enable signals for the write data

to the external memory. The ALTMEMPHY

megafunction converts the byte enables into

memory mem_dm signals. If mem_dm pins are not

required (mem_dm_pins set to FALSE), the

mem_dm

logic is not generated and the mem_dm

pins are not instantiated.

ctl_mem_cas_n_h

input

1

The column-address strobe signal from the

controller to the memory. Output during the high

half-period of the address and command clock and

driven by the memory controller.