Additional information, Revision history, Chapter info. additional information – Altera External Memory PHY Interface User Manual

Page 81

© January 2010

Altera Corporation

External Memory PHY Interface (ALTMEMPHY) (nonAFI) Megafunction User Guide

Additional Information

Revision History

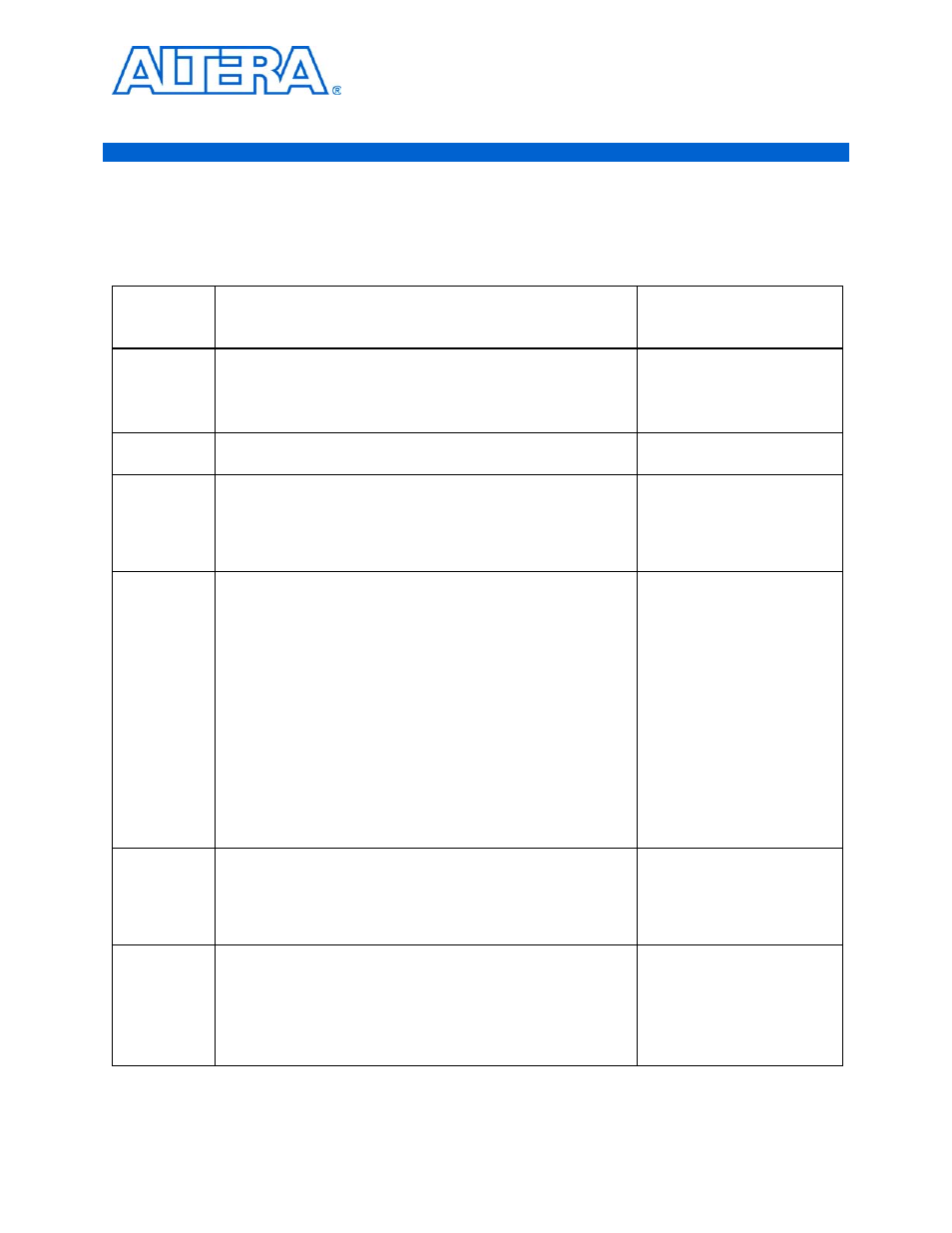

The table below displays the revision history for the chapters in this user guide.

Date and

Document

Version

Changes Made

Summary of Changes

January 2010,

v9.1 SP1

■

Removed AFI information and added AFI information references to

the External Memory Interface Handbook

■

Moved the nonAFI information to

Description—ALTMEMPHY (nonAFI)

—

June 2009,

v7.2

■

Added support for DDR3 SDRAM unbuffered DIMM multirank

memory configurations on Stratix III and Stratix IV devices

—

April 2009,

v7.1

■

Added DDR3 SDRAM without leveling

■

Added new signals:

aux_scan_clk_reset_n

PLL reconfiguration signals

—

March 2009,

v7.0

■

Included Arria II GX information

■

Updated generated files list

■

Updated AFI information

■

Moved nonAFI information to appendix

■

Added AFI timing diagrams for reads

■

Updated calibration process to indicate multiple chip select

calibration is supported by all devices

■

Added “DDR3 SDRAM (Discrete Device) and DDR2/DDR SDRAM

Calibration” section

■

Added clock sharing information

■

Changed pin_assignments.tcl description

■

Added section on dynamic OCT support

—

November

2008, v6.0

■

Included HardCopy IV information

■

Added Altera PHY interface (AFI) information

■

Amended HDL source file names to remove <device name>

■

Added ×36 emulation information

—

July 2008,

v5.0

■

Included HardCopy III and Stratix IV information

■

Updated to include changes in the Quartus II software version 8.0

■

Moved Appendix A to the end of Chapter 1

■

Updated all sections in Chapters 1, 2, and 3

■

Added Chapters 4, 5, 6, and 7

—