Altera External Memory PHY Interface User Manual

Page 29

Chapter 3: Functional Description—ALTMEMPHY (nonAFI)

3–13

ALTMEMPHY Signals

© January 2010

Altera Corporation

External Memory PHY Interface (ALTMEMPHY) (nonAFI) Megafunction User Guide

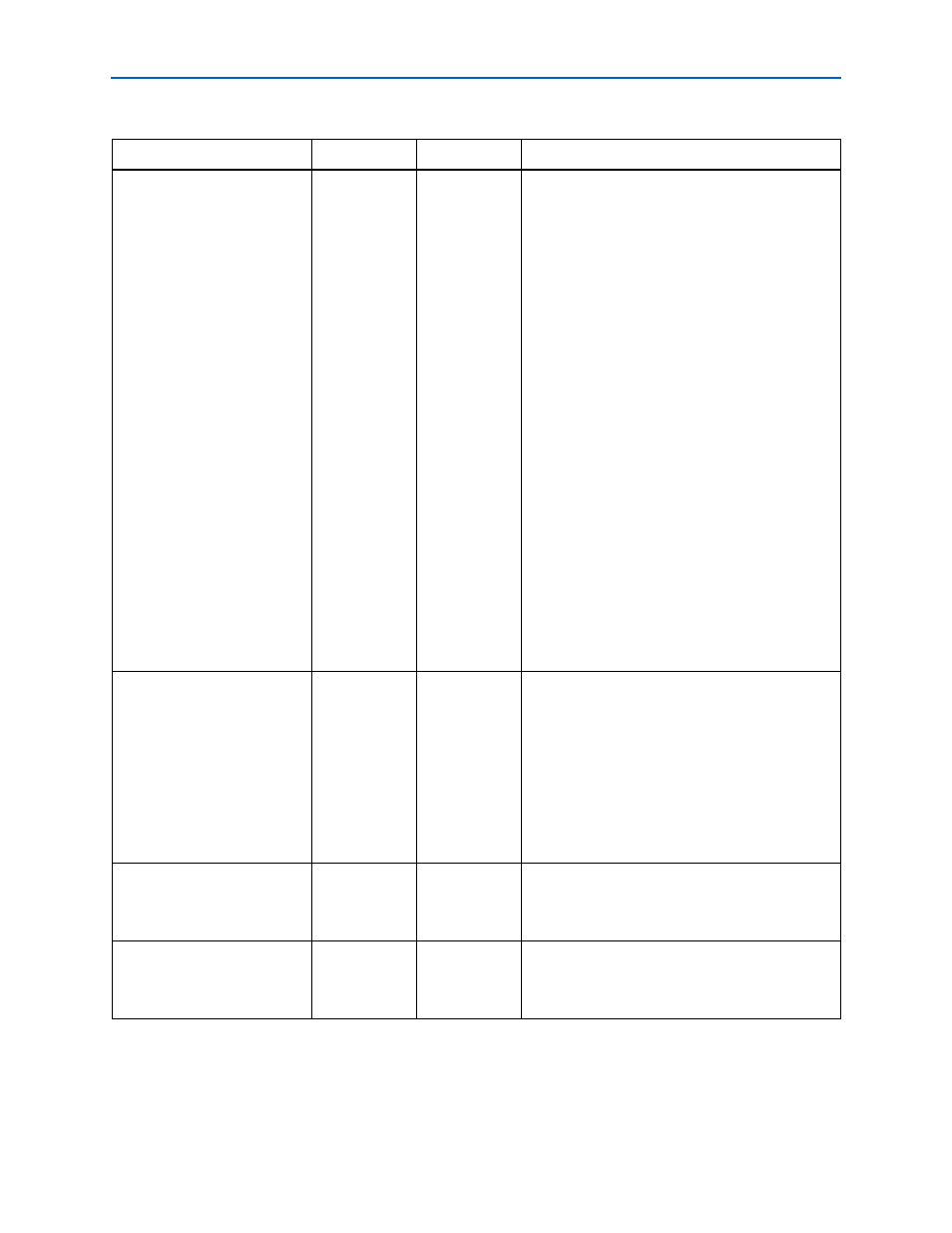

Table 3–6. Interface to the Memory Controller for DDR2 and DDR SDRAM—nonAFI

(Part 1 of 3)

Signal Name

Type

Width

Description

ctl_add_1t_ac_lat

input

1

When asserted, one extra address and command

clock cycle (1T) of latency is inserted in the address

and command path if the ADDR_CMD_ADD_1T

parameter is set to EXT_SELECT, see

Mechanism Between Write Commands and Write

Data” on page 3–49

For DDR SDRAM, the write latency is fixed at one

memory clock cycle, but for DDR2 SDRAM, this

value changes with the read CAS latency. As the

controller is running at half the rate of the memory

clock, a latency change of one controller clock cycle

is two memory clock cycles. The ALTMEMPHY

megafunction allows you to dynamically insert an

extra memory clock of delay in the address and

command path to compensate.

The insertion of delay is controlled by the

ADDR_CMD_ADD_1T

parameter and the

ctl_add_1t_ac_lat

signal. If

ADDR_CMD_ADD_1T

is set to the string

EXT_SELECT

, an extra cycle of latency can be

dynamically inserted on the address and command

outputs by asserting the ctl_add_1t_ac_lat

input, which allows run-time control of the address

and command latency. If ADDR_CMD_ADD_1T is

set to the string value TRUE, the extra clock cycle of

latency is always present. If it is set to the string

value FALSE, the extra latency is never added.

ctl_add_intermediate_

regs

Input

1

When asserted, an additional intermediate register or

registers is included in the address and command

path if the

ADDR_CMD_ADD_INTERMEDIATE_REGS

parameter is set to EXT_SELECT.

For Stratix II and Cyclone III devices only, to maintain

the clock cycle relationship between

address/command and the write data. You must

include the address/command phases where

required.

ctl_address

output

LOCAL_IF_

AWIDTH

The address corresponding to a write or read

request. The ALTMEMPHY sequencer logic drives

ctl_address

during calibration. ctl_address

has the same timing as local_address.

ctl_be

output

LOCAL_IF_

DWIDTH/8

The output to the controller indicating the

byte-enable flags. The ALTMEMPHY sequencer logic

drives ctl_be during calibration. ctl_be is

mandatory and has the same timing as local_be.