Table 3–15, Sram, Note 1) – Altera External Memory PHY Interface User Manual

Page 39

Chapter 3: Functional Description—ALTMEMPHY (nonAFI)

3–23

ALTMEMPHY Signals

© January 2010

Altera Corporation

External Memory PHY Interface (ALTMEMPHY) (nonAFI) Megafunction User Guide

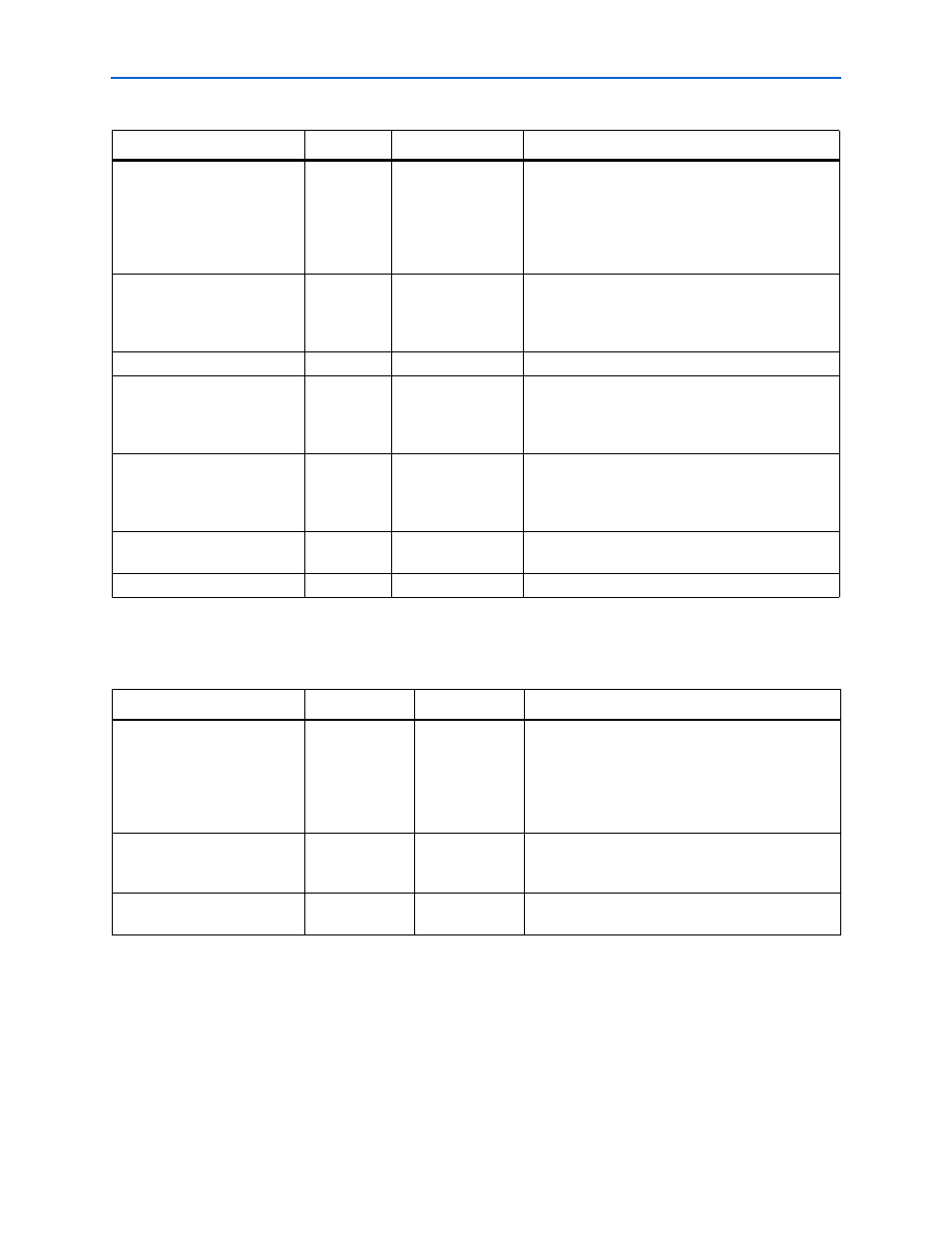

ctl_mem_be

input

LOCAL_IF_

DWIDTH ×

DWIDTH_

RATIO

Optional byte enable signals for the write data to the

external memory. The PHY converts the byte

enables into memory DM signals. If DM pins are not

required (MEM_DM_PINS set to FALSE), the DM

logic is not generated and the DM pins are not

instantiated.

ctl_mem_wdata

input

MEM_IF_

DWIDTH *

DWIDTH_

RATIO

The write data bus, which has valid data in the same

clock cycles that control_wdata_valid is

asserted.

ctl_mem_rdata_valid

output

1

Indicates when the ctl_mem_rdata is valid.

ctl_mem_wps_n

input

MEM_IF_CS_

WIDTH

Write enable signal from the controller to the

memory (QDR II SRAM). When this signal is

asserted, a write request is issued to the address

presented on the ctl_mem_addr_h port.

ctl_mem_rps_n

input

MEM_IF_CS_

WIDTH

Read enable signal from the controller to the

memory (QDR II SRAM). When this signal is

asserted, a read request is issued to the address

presented on the ctl_mem_addr_l port.

ctl_mem_rdata

output

LOCAL_IF_

DWIDTH

Captured, resynchronized, and de-multiplexed read

data from the PHY to the controller.

ctl_mem_wdata_valid

input

1

Generates the DQ output enable.

Note to

:

(1) Address and command and wdata/rdata.

Table 3–14. Datapath Interface for QDR II+/QDR II SRAM

(Note 1)

(Part 2 of 2)

Signal Name

Type

Width

Description

Table 3–15. Calibration Status Signals for QDR II+/QDR II SRAM

Signal Name

Type

Width

Description

ctl_usr_mode_rdy

output

1

Active high signal specifying the PHY has finished

its calibration and is ready to accept user read or

write requests. This signal does not indicate that

calibration was successful, so you must check

whether resynchronization_successful

is high also.

resynchronisation_

successful

output

1

Active high signal that shall be set to indicate that

calibration of the read data resynchronization clock

phase was successful.

ctl_rlat

output

5

Indicates the read latency of the interface in PHY

clock cycles.

Note to

:

(1) Calibration control or passed through from the user interface.