Clock and reset management –3, Clock and reset management – Altera External Memory PHY Interface User Manual

Page 71

Chapter 4: Support for Arria GX, HardCopy II, Stratix II, and Stratix II GX Devices

4–3

DDR2/DDR SDRAM

© January 2010

Altera Corporation

External Memory PHY Interface (ALTMEMPHY) (nonAFI) Megafunction User Guide

Read Data Alignment

Data alignment is the process controlled by the sequencer to ensure the correct

captured read data is present in the same half-rate clock cycle at the output of the read

data DPRAM. Data alignment is implemented using either M4K or M512K memory

blocks. The bottom of

shows the concatenation of the read data into valid

HDR data.

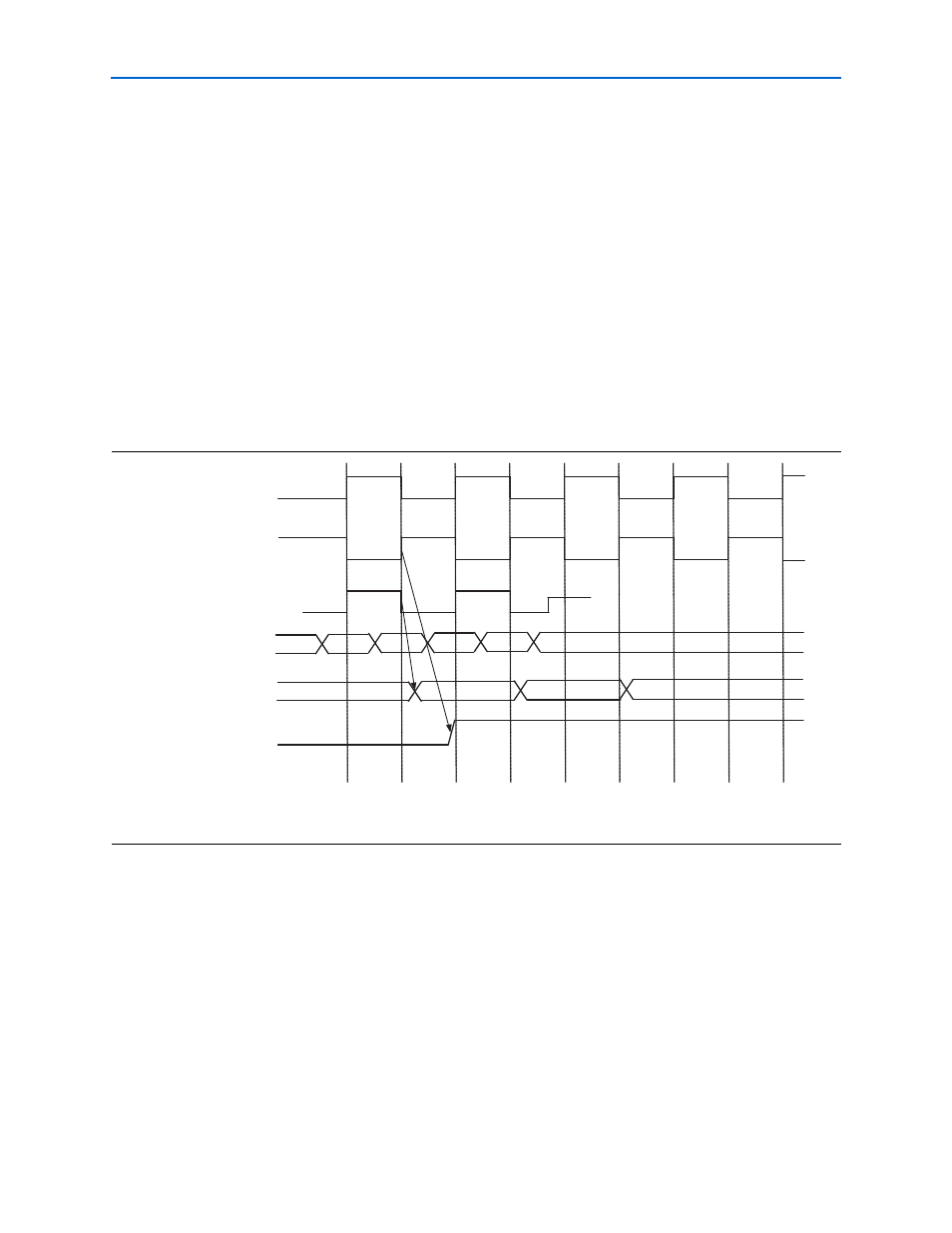

Postamble Protection

The ALTMEMPHY megafunction provides the DQS postamble logic. The postamble

clock is derived from the resynchronization clock and is the negative edge of the

resynchronization clock. The ALTMEMPHY megafunction calibrates the

resynchronization clock such that it is in the center of the data-valid window. The

clock that controls the postamble logic, the postamble clock, is the negative edge of

the resynchronization clock. No additional clocks are required.

shows the

relationship between the postamble clock and the resynchronization clock.

f

For more information about the postamble circuitry, refer to the

chapter in the Stratix II Device Handbook.

Clock and Reset Management

The clocking and reset block is responsible for clock generation, reset management,

and phase shifting of clocks. It also has control of clock network types that route the

clocks.

Figure 4–2. Relationship Between Postamble Clock and Resynchronization Clock

Note to

(1) resync_clk_2x is delayed further to allow for the I/O element (IOE) to core transition time.

resync_clk_2x

postamble_clk

H1

H2

L2

L1

dqs (90˚ shifted)

dq

Data input to resync reg's

ARST at postamble reg's

H1L1

H2L2