Calibration status interface, Additional calibration status interface signals – Altera External Memory PHY Interface User Manual

Page 56

3–40

Chapter 3: Functional Description—ALTMEMPHY (nonAFI)

Additional Debug Signals

External Memory PHY Interface (ALTMEMPHY) (nonAFI) Megafunction User Guide

© January 2010

Altera Corporation

■

pll_reconfig_busy

■

pll_reconfig_clk

■

pll_reconfig_data_out

■

pll_reconfig_reset

1

For full description of the signals listed and their required operation, refer to the

respective Device Handbooks or

.

1

The output clock order is fixed in the ALTMEMPHY (seq_pll_select) and a

mapping takes place to align with the required clock port used for each different

device family. Refer to <variation name>_phy_alt_mem_phy.v(hd) file and refer to the

section that starts with the following code:

// NB This lookup table shall be different for CIII/SIII

// The PLL phasecounterselect is 3 bits wide, therefore hardcode the

output to 3 bits:

Calibration Status Interface

The following calibration signals provide information for ALTMEMPHY

megafunction:

■

ctl_cal_success

indicates calibration success

■

ctl_cal_fail

indicates calibration failure

Additional Calibration Status Interface Signals

Add the signals in

to your simulation to provide additional information

about calibration status:

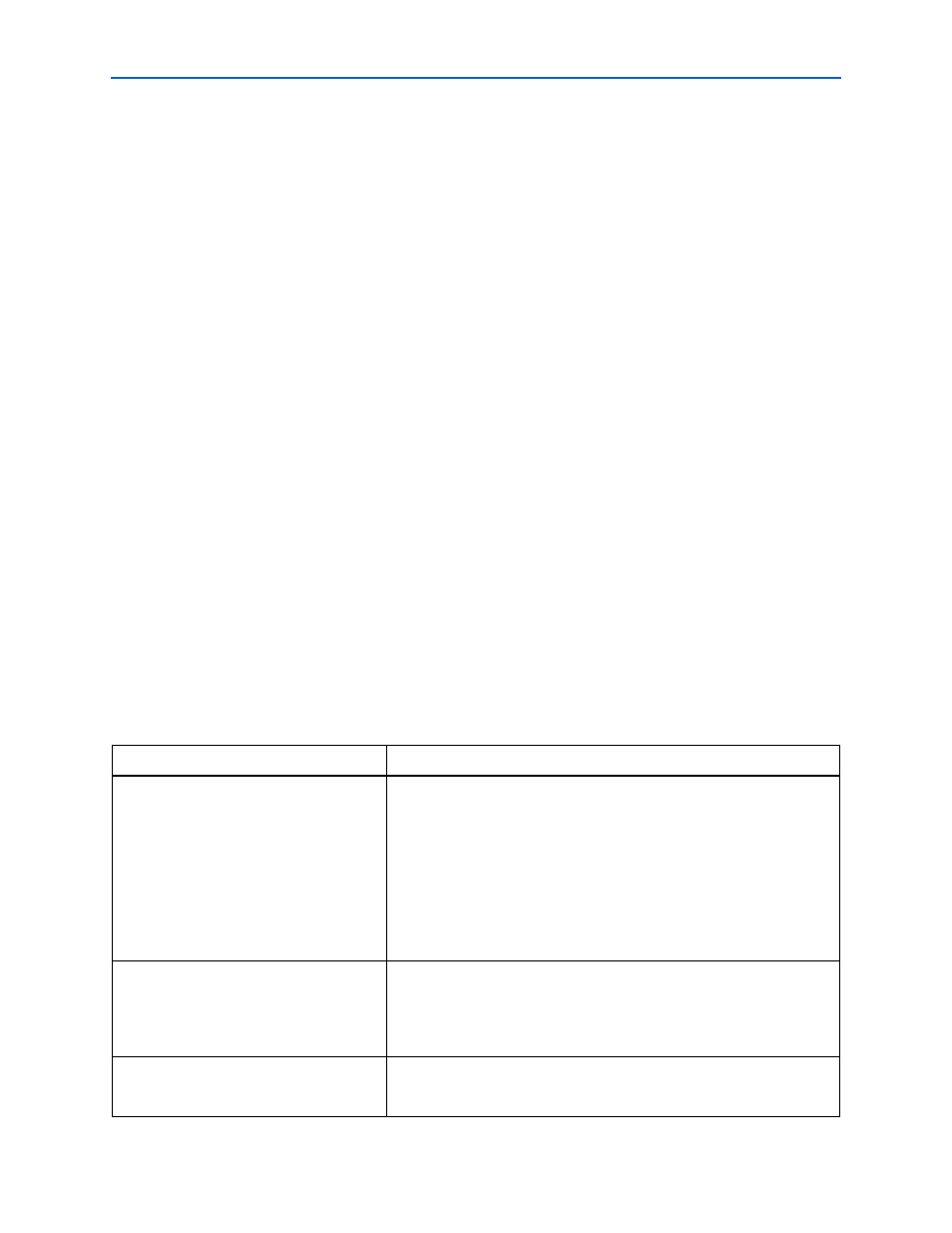

Table 3–17. Signals for Calibration Status

Signal

Description

rsu_codvw_phase

(Center of data valid window)

The ALTMEMPHY resynchronization setup unit (RSU) sweeps the phase of a

resynchronization clock across 360° (full-rate mode) or 720° (half-rate

mode) of a memory clock cycle. Data reads from the DIMM are performed

for each phase position, and a data valid window is located, which is the set

of resynchronization clock phase positions where data is successfully read.

The final resynchronization clock phase is set at the center of this range: the

center of the data valid window or CODVW. This output is set to the current

calculated value for the CODVW, and represents how many phase steps

were performed by the PLL to offset the resynchronization clock from the

memory clock.

rsu_read_latency

(Read latency at the center of the window)

If the RSU can find one data valid window (and not more than one) then the

resynchronization clock is positioned at the center and the

rsu_read_latency

output is then set to the read latency (in phy_clk

cycles) using that resynchronization clock phase. If calibration is

unsuccessful then this signal remains at 0.

rsu_no_dvw_err

(Calibration failed due to no window found)

If the RSU sweeps the resynchronization clock across every phase and does

not see any valid data at any phase position, then calibration fails and this

output is set to 1.