Ddr2 sdram, Ddr2 sdram –6, Ecc –6 – Altera DDR SDRAM High-Performance Controllers and ALTMEMPHY IP User Manual

Page 100

6–6

Chapter 6: Functional Description—High-Performance Controller II

Controller Features Descriptions

External Memory Interface Handbook Volume 3

June 2011

Altera Corporation

Section I. DDR and DDR2 SDRAM Controllers with ALTMEMPHY IP User Guide

DDR2 SDRAM

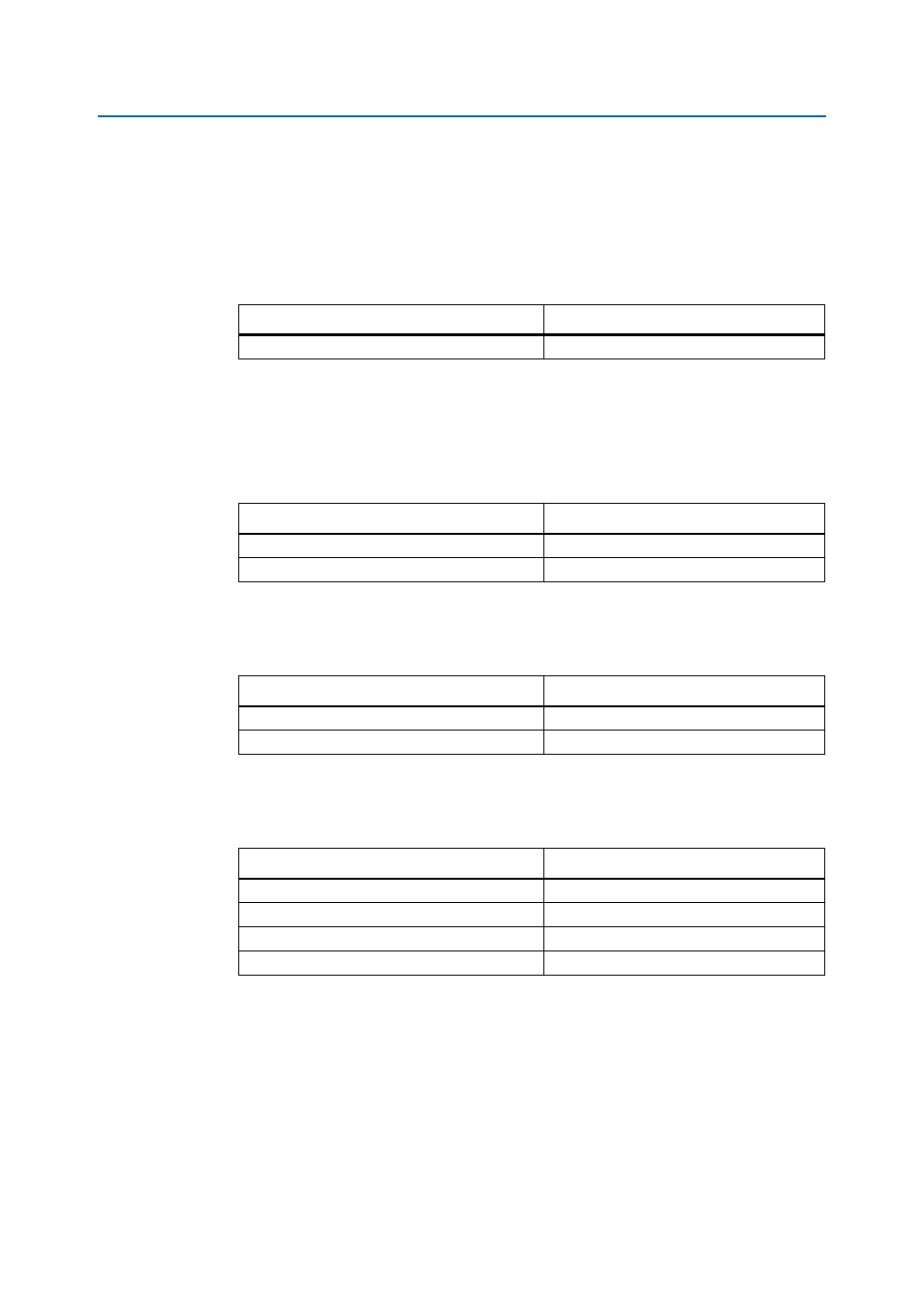

Table 6–1

shows which ODT signal is enabled for single-slot single chip-select per

DIMM.

1

There is no ODT for reads.

Table 6–2

shows which ODT signal is enabled for single-slot dual chip-select per

DIMM.

1

There is no ODT for reads.

Table 6–3

shows which ODT signal is enabled for dual-slot single chip-select per

DIMM.

Table 6–4

shows which ODT signal is enabled for dual-slot dual chip-select per

DIMM.

ECC

The ECC logic comprises an encoder and a decoder-corrector, which can detect and

correct single-bit errors, and detect double-bit errors. The ECC logic is available in

widths of 16, 24, 40, and 72 bits. The ECC logic has the following features:

■

Has Hamming code ECC logic that encodes every 64, 32, 16, or 8 bits of data into

72, 40, 24, or 16 bits of codeword.

Table 6–1. ODT—DDR2 SDRAM Single Slot Single Chip-select Per DIMM (Write)

Write On

ODT Enabled

mem_cs[0]

mem_odt[0]

Table 6–2. ODT—DDR2 SDRAM Single Slot Dual Chip-select Per DIMM (Write)

Write On

ODT Enabled

mem_cs[0]

mem_odt[0]

mem_cs[1]

mem_odt[1]

Table 6–3. ODT—DDR2 SDRAM Dual Slot Single Chip-select Per DIMM (Write)

Write On

ODT Enabled

mem_cs[0]

mem_odt[1]

mem_cs[1]

mem_odt[0]

Table 6–4. ODT—DDR2 SDRAM Dual Slot Dual Chip-select Per DIMM (Write)

Write On

ODT Enabled

mem_cs[0]

mem_odt[2]

mem_cs[1]

mem_odt[3]

mem_cs[2]

mem_odt[0]

mem_cs[3]

mem_odt[1]