Completing the qsys system, Completing the qsys system –5 – Altera DDR SDRAM High-Performance Controllers and ALTMEMPHY IP User Manual

Page 19

Chapter 2: Getting Started

2–5

Qsys Flow

June 2011

Altera Corporation

External Memory Interface Handbook Volume 3

Section I. DDR and DDR2 SDRAM Controllers with ALTMEMPHY IP User Guide

6. Click Finish to complete parameterizing the DDR or DDR2 SDRAM Controller

with ALTMEMPHY IP and add it to the system.

Completing the Qsys System

To complete the Qsys system, perform the following steps:

1. In the Component Library tab, select Nios II Processor and click Add.

2. On the Nios II Processor page, in the Core Nios II tab, select altmemddr for Reset

Vector

and Exception Vector.

3. Change the Reset Vector Offset and the Exception Vector Offset to an Avalon

address that is not written to by the ALTMEMPHY megafunction during its

calibration process.

c

The ALTMEMPHY megafunction performs memory interface calibration

every time it is reset, and in doing so, writes to a range of addresses. If you

want your memory contents to remain intact through a system reset, you

should avoid using these memory addresses. This step is not necessary if

you reload your SDRAM memory contents from flash every time you reset

your system.

To calculate the Avalon-MM address equivalent of the memory address range 0×0

to 0×1f, multiply the memory address by the width of the memory interface data

bus in bytes. Refer to

for more Avalon-MM addresses.

4. Click Finish.

5. On the Component Library tab, expand Interface Protocols and expand Serial.

6. Select JTAG UART and click Add.

7. Click Finish.

1

If there are warnings about overlapping addresses, on the System menu,

click Auto Assign Base Addresses.

If you enable ECC and there are warnings about overlapping IRQs, on the

System menu click Auto Assign IRQs.

8. For this example system, ensure all the other modules are clocked on the

altmemddr_sysclk

, to avoid any unnecessary clock-domain crossing logic.

9. Click Generate.

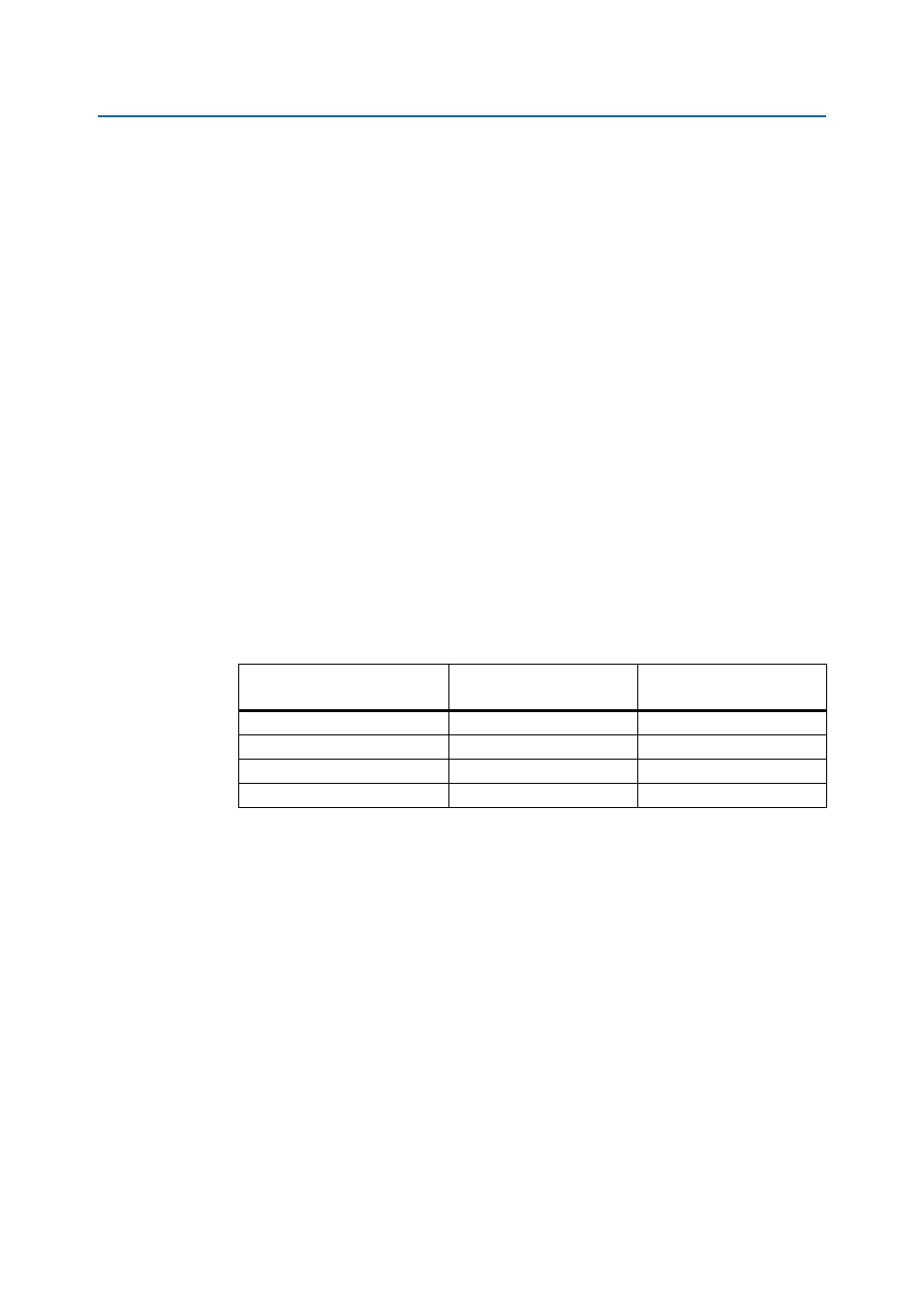

Table 2–2. Avalon-MM Addresses for AFI Mode

External Memory Interface

Width

Reset Vector Offset

Exception Vector Offset

8

0×40

0×60

16

0×80

0×A0

32

0×100

0×120

64

0×200

0×220