Altera DDR SDRAM High-Performance Controllers and ALTMEMPHY IP User Manual

Page 115

Chapter 6: Functional Description—High-Performance Controller II

6–21

Example Top-Level File

June 2011

Altera Corporation

External Memory Interface Handbook Volume 3

Section I. DDR and DDR2 SDRAM Controllers with ALTMEMPHY IP User Guide

■

Low-power mode operation

The example driver requests the controller to place the memory into power-down

and self-refresh states, and hold it in those states for the amount of time specified

by the COUNTER_VALUE signal. You can vary this value to adjust the duration the

memory is kept in the low-power states. This test is only available if your

controller variation enables the low-power mode option.

The example driver has four outputs that allow you to observe which tests are

currently running and if the tests are passing. The pass not fail (pnf) signal goes low

once one or more errors occur and remains low. The pass not fail per byte

(pnf_per_byte) signal goes low when there is incorrect data in a byte but goes back

high again once correct data is observed in the following byte. The test_status signal

indicates the test that is currently running, allowing you to determine which test has

failed. The test_complete signal goes high for a single clock cycle at the end of the set

of tests.

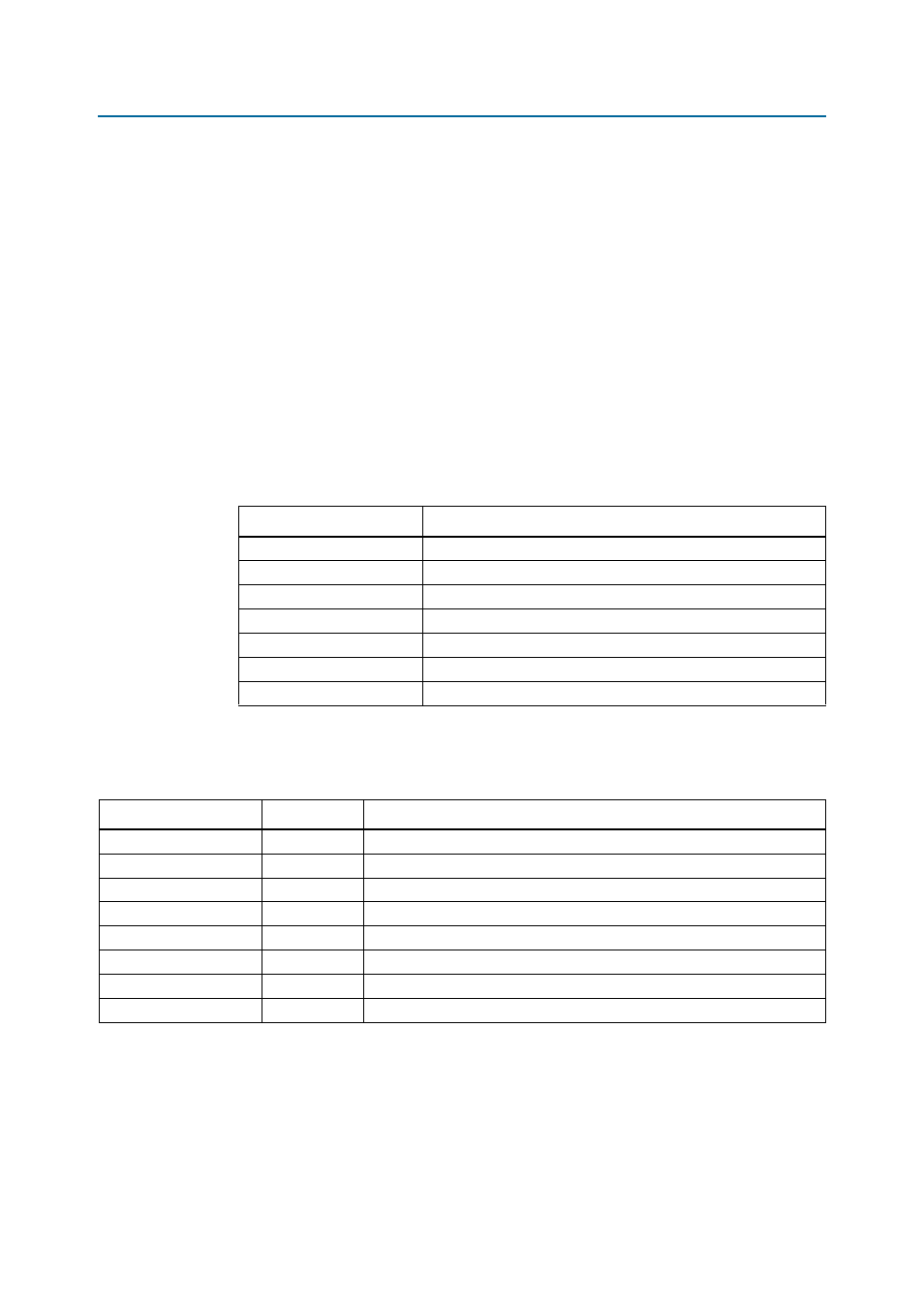

Table 6–11

shows the bit mapping for each test status.

shows the ALTMEMPHY Debug interface signals, which are located in

<variation_name>_phy.v/vhd file.

Table 6–11. Test Status[] Bit Mapping

Bit

Test

0

Sequential address test

1

Incomplete write test

2

Data mask pin test

3

Address pin test

4

Power-down test

5

Self-refresh test

6

Auto-precharge test

Table 6–12. ALTMEMPHY Debug Interface Signals

Signal Name

Direction

Description

dbg_clk

Input

Debug interface clock

dbg_addr

Input

Debug interface address

dbg_cs

Input

Debug interface chip select

dbg_wr

Input

Debug interface write request

dbg_wr_data

Input

Debug interface write data

dbg_rd

Input

Debug interface read request

dbg_rd_data

Input

Debug interface read data

dbg_waitrequest

Output

Debug interface wait request