Cyclone iii devices, Cyclone iii devices –23 – Altera DDR SDRAM High-Performance Controllers and ALTMEMPHY IP User Manual

Page 69

Chapter 5: Functional Description—ALTMEMPHY

5–23

Block Description

June 2011

Altera Corporation

External Memory Interface Handbook Volume 3

Section I. DDR and DDR2 SDRAM Controllers with ALTMEMPHY IP User Guide

Cyclone III Devices

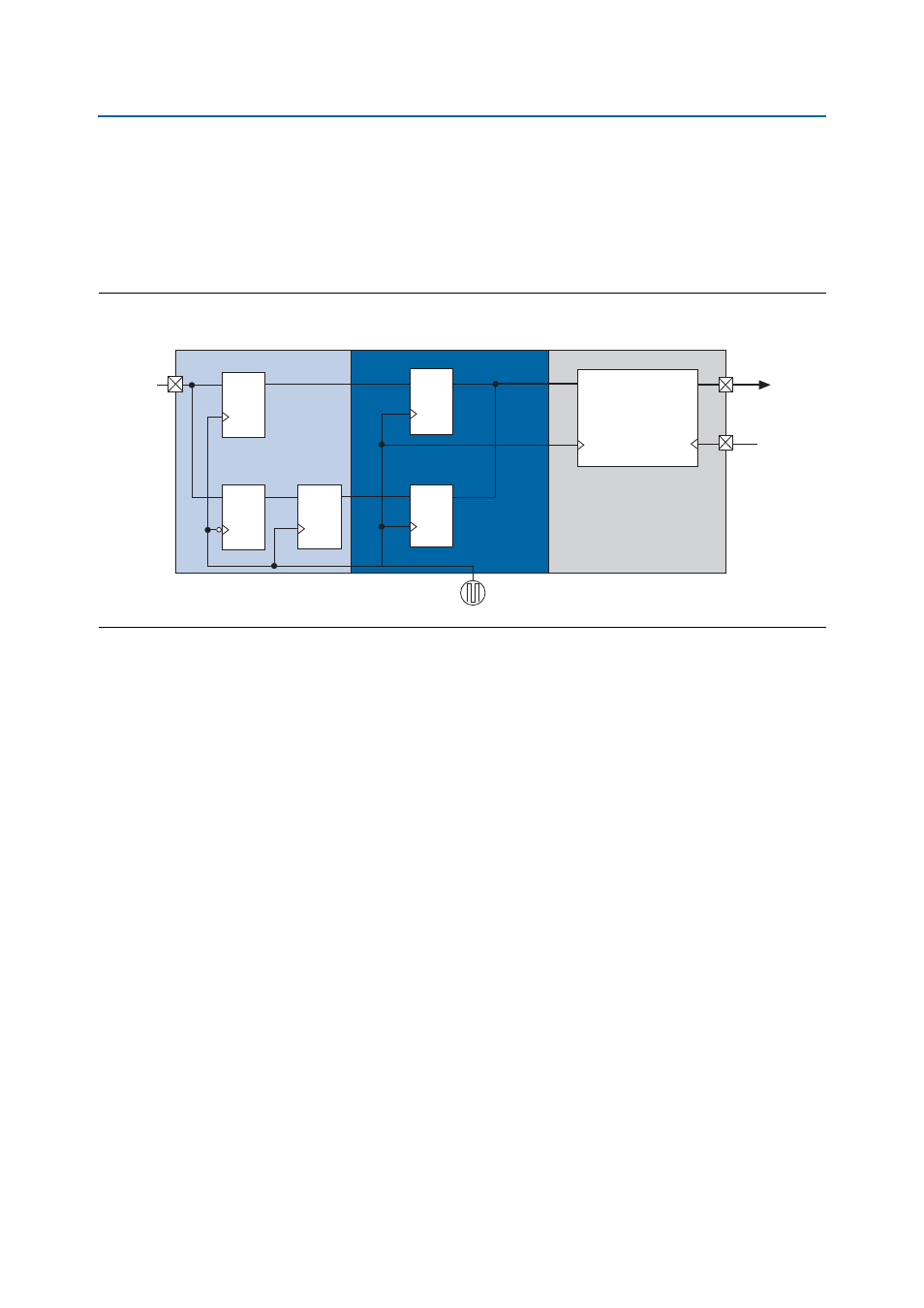

Figure 5–7

shows the Cyclone III read datapath for a single DQ pin. The diagram

shows a half-rate read path where four data bits are produced for each DQ pin. Unlike

Stratix II and Stratix III devices, data capture is entirely done in the core logic because

the I/O element (IOE) does not contain DDIO capture registers (nonDQS capture).

The full-rate read datapath for Cyclone III devices is similar to the half-rate

Cyclone III implementation, except that the data is read out of the FIFO buffer with a

full-rate clock instead of a half-rate clock.

Capture and Pipelining

The DDR and DDR2 SDRAM read data is captured using registers in the Cyclone III

FPGA core. These capture registers are clocked using the capture clock

(resynch_clk_2x). The captured read data generates two data bits per DQ pin; one

data bit for the read data captured by the rising edge of the capture clock and one data

bit for the read data captured by the falling edge of the capture clock.

After the read data has been captured, it may be necessary to insert registers in the

read datapath between the capture registers and the read data FIFO buffer to help

meet timing. These registers are known as pipeline registers and are clocked off the

same clock used by the capture registers, the capture clock (resync_clk_2x).

Data Demultiplexing

The data demultiplexing for Cyclone III devices is instantiated in the same way as it is

with Stratix II devices.

Postamble Protection

Postamble protection circuitry is not required in the Cyclone III device

implementation as DQS mode capture of the DQ data is not supported. The data

capture is done using the clock (resync_clk_2x) generated from the ALTPLL

megafunction.

Figure 5–7. Cyclone III Read Datapath

DQ

resync_clk_2x

FIFO

wr_data

rd_data

4-bits

phy_clk

read_data

Data Capture

Data Pipeline Registers

Data Demux & Alignment

D

Q

D

Q

D

Q

D

Q

D

Q