Memory side-band signals, Self-refresh (low power) interface, User-controller refresh interface – Altera DDR SDRAM High-Performance Controllers and ALTMEMPHY IP User Manual

Page 104: Configuration and status register (csr) interface, Memory side-band signals –10

6–10

Chapter 6: Functional Description—High-Performance Controller II

External Interfaces

External Memory Interface Handbook Volume 3

June 2011

Altera Corporation

Section I. DDR and DDR2 SDRAM Controllers with ALTMEMPHY IP User Guide

Memory Side-Band Signals

This section describes supported side-band signals.

Self-Refresh (Low Power) Interface

The optional low power self-refresh interface consists of a request signal and an

acknowledgement signal, which you can use to instruct the controller to place the

memory device into self-refresh mode. This interface is clocked by afi_clk.

When you assert the request signal, the controller places the memory device into

self-refresh mode and asserts the acknowledge signal. To bring the memory device

out of self-refresh mode, you deassert the request signal; the controller then deasserts

the acknowledge signal when the memory device is no longer in self-refresh mode.

User-Controller Refresh Interface

The optional user-controlled refresh interface consists of a request signal and an

acknowledgement signal, which allow you to determine when the controller issues

refresh signals to the memory device. This interface gives you increased control over

worst-case read latency, and enables you to issue refresh bursts during idle periods.

This interface is clocked by afi_clk.

When you assert a refresh request signal to instruct the controller to perform a refresh

operation, that request takes priority over any outstanding read or write requests that

might be in the command queue. Once the controller successfully issues a refresh

command to the memory device, the controller asserts the refresh acknowledge signal

for one clock cycle.

If you want to send consecutive refresh commands, you should keep the refresh

request asserted, which causes the controller to issue another refresh command and

again assert the acknowledge signal for a one clock cycle. You can perform up to nine

consecutive refresh commands.

Configuration and Status Register (CSR) Interface

The controller has a configuration and status register (CSR) interface that allows you

to configure timing parameters, address widths, and the behavior of the controller.

The CSR interface is a 32-bit Avalon-MM slave of fixed address width; if you do not

need this feature, you can disable it to save area.

This interface is clocked by csr_clk, which is the same as afi_clk, and is always

synchronous relative to the main data slave interface.

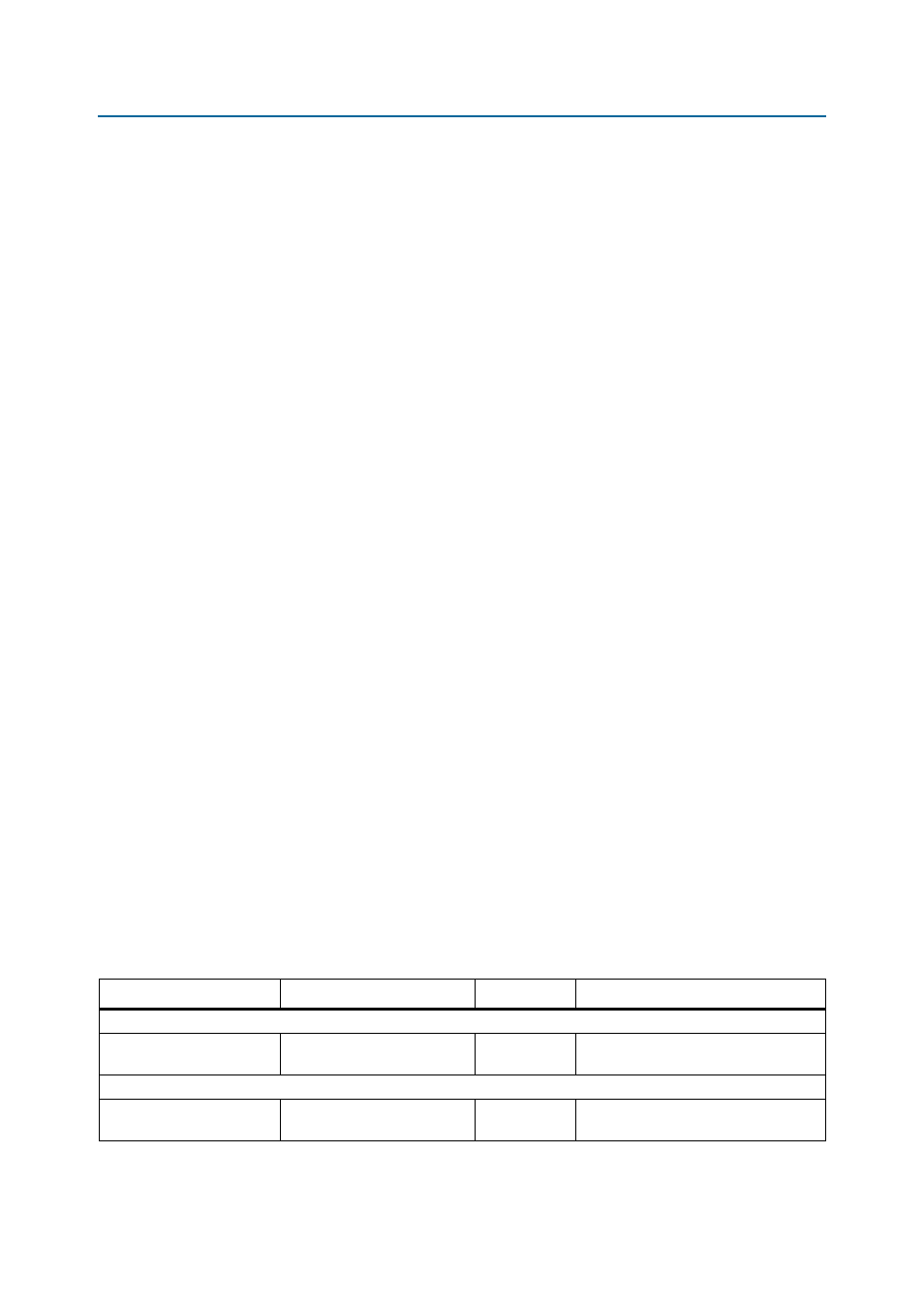

Table 6–5

summarizes the controller’s external interfaces.

Table 6–5. Summary of Controller External Interfaces (Part 1 of 2)

Interface Name

Display Name

Type

Description

Clock and Reset Interface

Clock and Reset Interface

Clock and Reset Interface

AFI

(1)

Clock and reset generated by UniPHY to

the controller.

Avalon-ST Data Slave Interface

Command Channel

Avalon-ST Data Slave Interface

Avalon-ST

(2)

Address and command channel for read

and write, SCSD.