Altera DDR SDRAM High-Performance Controllers and ALTMEMPHY IP User Manual

Page 64

5–18

Chapter 5: Functional Description—ALTMEMPHY

Block Description

External Memory Interface Handbook Volume 3

June 2011

Altera Corporation

Section I. DDR and DDR2 SDRAM Controllers with ALTMEMPHY IP User Guide

Clock and reset management for full-rate designs is similar to half-rate support (see

Table 5–4 on page 5–17

). The PLL is configured exactly in the same way as for

half-rate support. The mem_clk_2x output acts as the PHY full-rate clock. Also, instead

of going through the I/O clock divider, the resync_clk_2x output is now directly

connected to the resynchronization registers. The rest of the PLL outputs are

connected in the same way as for half-rate support.

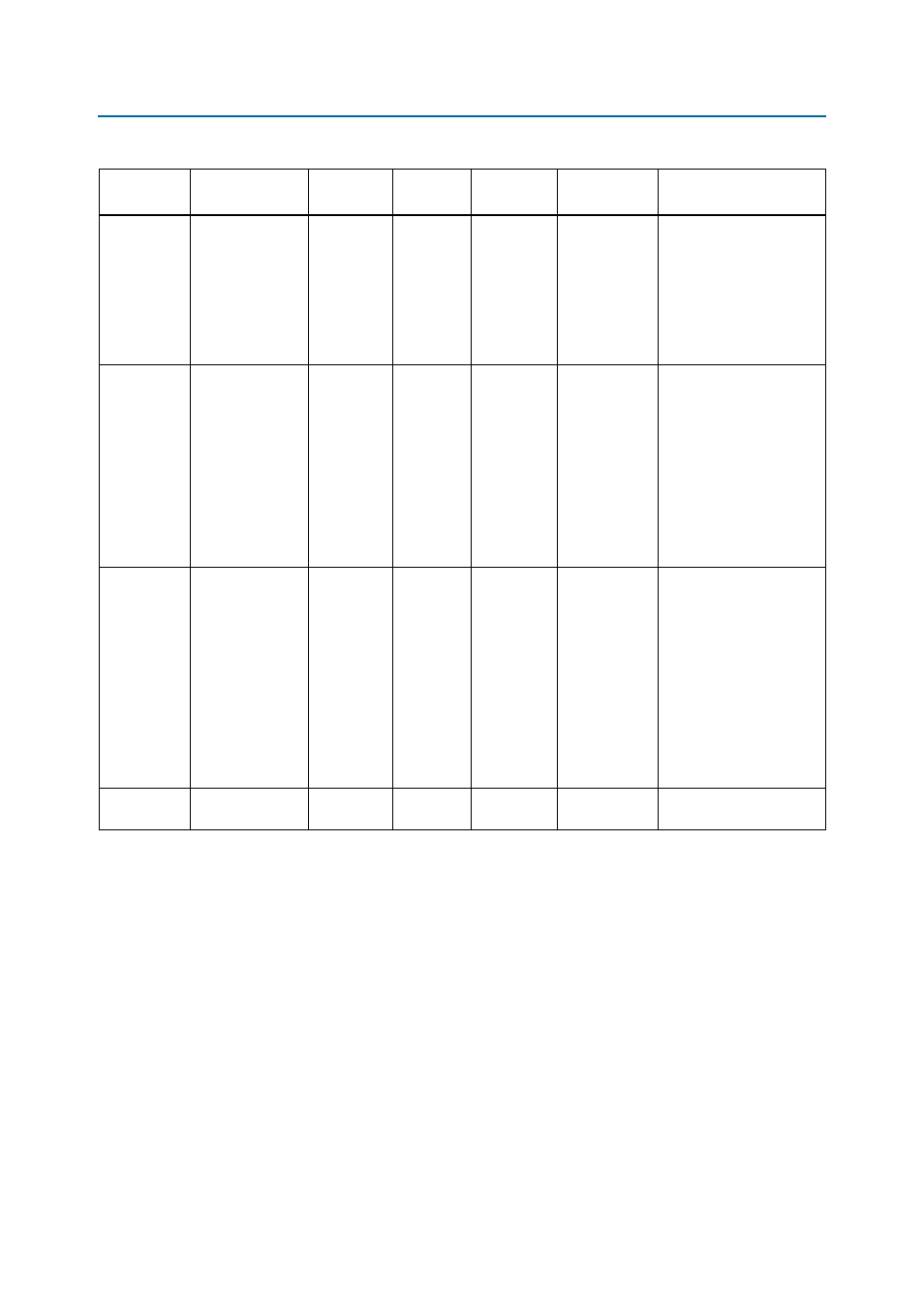

Half-rate and

full-rate

write_clk_

2x

C3

–90

Full-Rate

Dual regional

Clocks the data out of the

double data rate

input/output (DDIO) pins

in advance of the DQS

strobe (or equivalent). As

a result, its phase leads

that of the mem_clk_2x

clock by 90°.

Half-rate and

full-rate

resync_clk_

2x

C4

Calibrated

Full-Rate

Dual regional

This clock feeds the I/O

clock divider that then

clocks the

resynchronization

registers after the capture

registers. Its phase is

adjusted in the calibration

process. You can use an

inverted version of this

clock for postamble

clocking.

Half-rate and

full-rate

measure_clk_1x

(2)

C5

Calibrated

Half-Rate

Dual regional

This clock is for VT

tracking. This free-running

clock measures relative

phase shifts between the

internal clock(s) and those

being fed back through a

mimic path. As a result,

the ALTMEMPHY

megafunction can track VT

effects on the FPGA and

compensate for the

effects.

Half-rate and

full-rate

ac_clk_1x

C6

Set in the

GUI

Half-Rate

Dual regional

Address and command

clock.

Notes to

Table 5–4

:

(1) In full-rate designs a _1x clock may run at full-rate clock rate.

(2) This clock should be of the same clock network clock as the resync_clk_2x clock.

Table 5–4. DDR2 SDRAM Clocking in Stratix IV and Stratix III Devices (Part 2 of 2)

Design Rate

Clock Name

(1)

Postscale

Counter

Phase

(Degrees)

Clock Rate

Clock Network

Type

Notes