Half-rate read, Half-rate read –2 – Altera DDR SDRAM High-Performance Controllers and ALTMEMPHY IP User Manual

Page 130

8–

2

Ch

apt

er

8:

T

imin

g

Diagr

a

ms

D

D

R

an

d DDR

2 Hi

gh

-P

erfo

rmance Controllers

II

Ex

ternal Memory

Interfac

e H

andbook

Volu

me 3

Jun

e

2

011

Al

tera Cor

por

atio

n

Secti

o

n

I.

D

DR an

d DDR

2 SDR

A

M Co

ntr

o

lle

rs with ALTMEMPH

Y IP

User G

u

ide

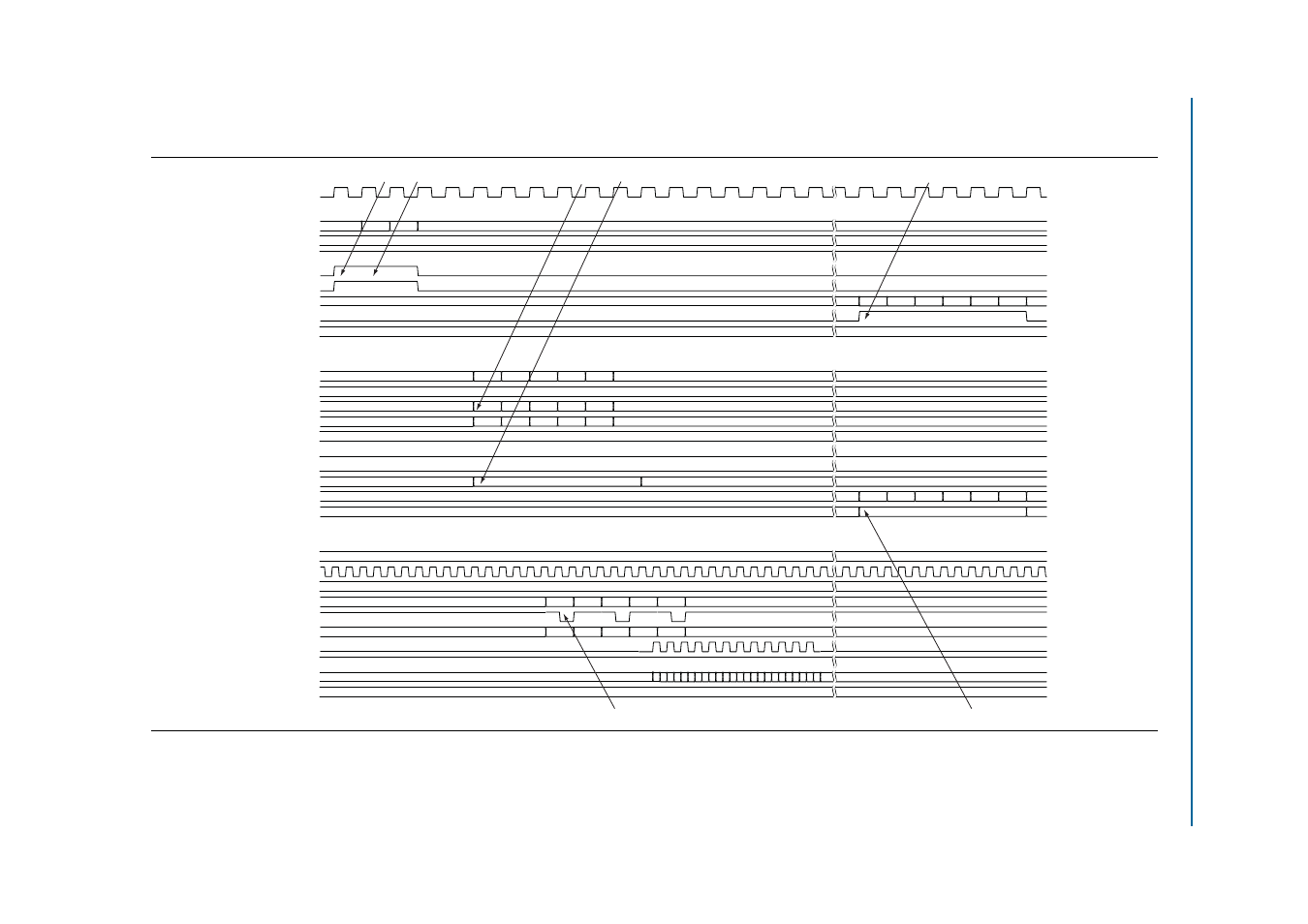

Half-Rate Read

The following sequence corresponds with the numbered items in

Figure 8–1. Half-Rate Read Operation for HPC II

phy_clk

Local Interface

local_address[25:0]

local_size[4:0]

local_ready

local_burstbegin

local_read_req

local_rdata[31:0]

local_rdata_valid

local_be[3:0]

afi_addr[27:0]

Controller - AFI

afi_ba[5:0]

afi_cs_n[3:0]

AFI Command[2:0]

afi_dm[3:0]

afi_dqs_burst[0]

afi_dqs_burst[1]

afi_doing_rd[1:0]

afi_rdata[31:0]

afi_rdata_valid[1:0]

mem_cke[1:0]

AFI Memory Interface

mem_clk

mem_ba[2:0]

mem_addr[13:0]

mem_cs_n[0]

Mem Command[2:0]

mem_dqs

mem_dm

mem_dq[7:0]

mem_odt[1:0]

0000002

0000000

2

0000004

0000000

AABBCCDD EEFF0011 AABBCCDD EEFF0011 AABBCCDD EEFF0011

0000000 0000000 0000008 0000000

0

0000010

0000000

B

F

B

F

B

RD

NOP

RD

NOP

RD

F

3

F

3

AABBCCDD EEFF0011 AABBCCDD EEFF0011 AABBCCDD EEFF0011

0000

0000

0008

0000

0

0010

RD

NOP

NOP

NOP

RD

NOP

RD

DDCCBB AA 11 00 FF EE DDCCBB AA 11 00 FF EE DDCCBB AA 11 00 FF EE

[5]

[6]

[1]

[2]

[3]

[4]

[7]