Cyclone iii devices, Cyclone iii devices –13 – Altera DDR SDRAM High-Performance Controllers and ALTMEMPHY IP User Manual

Page 59

Cha

p

te

r 5

:

F

unc

tio

nal

Descr

ipt

ion

—

ALTM

EMPHY

5–1

3

Block Des

cription

Jun

e 2

011

Al

tera

Cor

por

ation

E

xter

nal

Mem

o

ry

Inter

face H

an

dbo

ok Volu

me 3

Secti

on I.

D

D

R

and D

D

R

2

SDR

A

M Contr

o

ller

s wi

th ALTM

EMPH

Y

IP User

G

u

id

e

Cyclone III Devices

Clock management circuitry is implemented using the ALTPLL megafunction.

The ALTPLL megafunction is instantiated within the ALTMEMPHY megafunction and is responsible for generating all the

clocks used by the ALTMEMPHY megafunction and the memory controller.

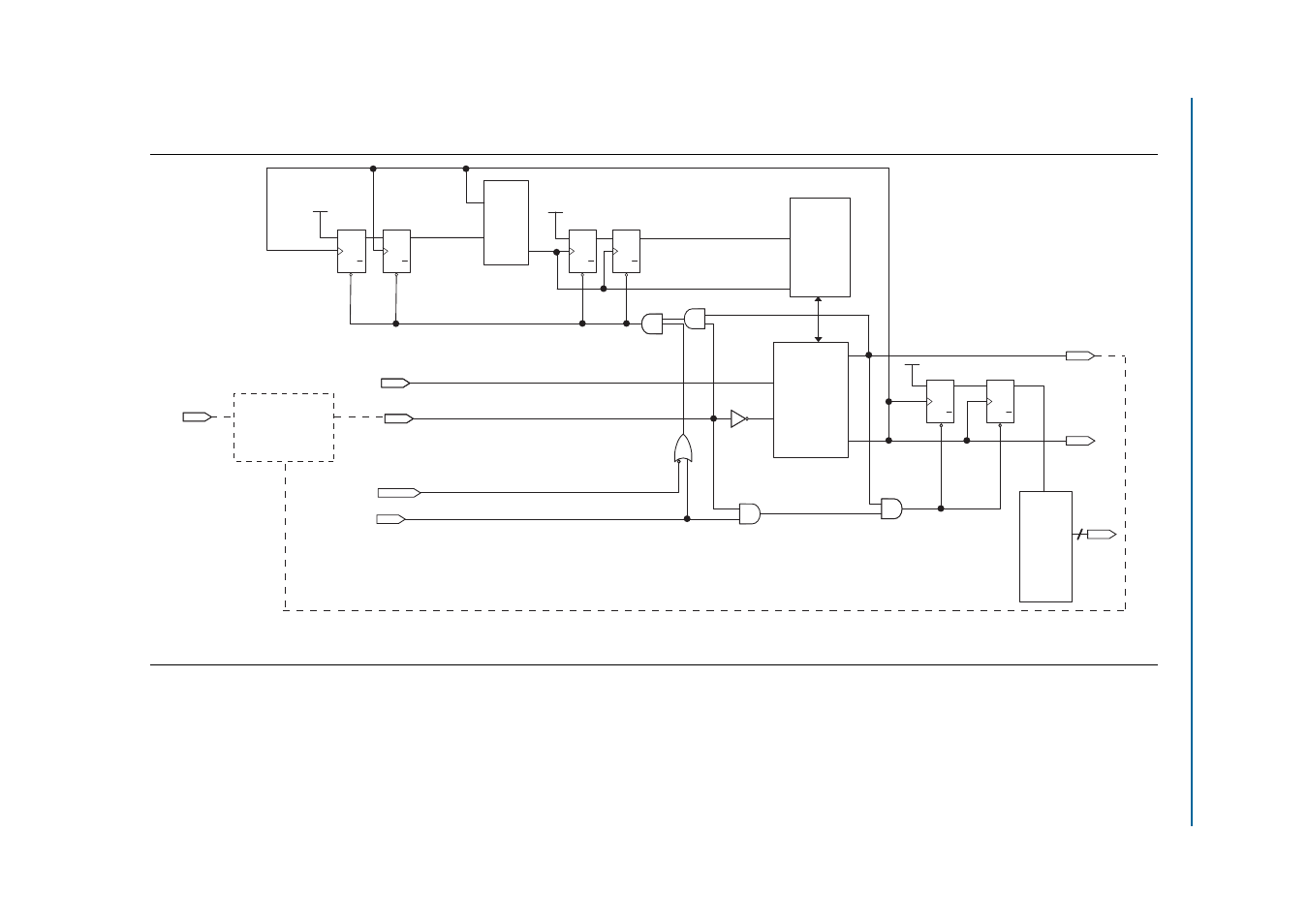

Figure 5–3. ALTMEMPHY Reset Management Block for Arria GX, Arria II GX, Cyclone III, HardCopy II, Stratix II, and Stratix II GX Devices

(Note 1)

Note to

Figure 5–3

:

(1) The reset circuit for Arria II GX and Cyclone III devices have no PLL reconfig block.

PLL

Q

Q

SET

CLR

D

Q

Q

SET

CLR

D

Q

Q

SET

CLR

D

Q

Q

SET

CLR

D

Q

Q

SET

CLR

D

PLL

reconfig

Q

Q

SET

CLR

D

soft_reset_n

global_reset_n

pll_ref_clk

phy_clk_out

reset_request_n

phy_internal_reset_n

areset (active HIGH)

pll_reconfig_reset_ams_n

pll_reconfig_reset_ams_n_r

refclk

c0

locked

reset_master_ams

scan_clk

reset

global_pre_clear

Reset

pipes

PHY resets

pll_reset

pll_locked

Optional

reset_request_n

edge detect and

reset counter

Another

system

clock

clk_divider_reset_n

clk

divider

circuit

phy_clk

reset_n

scan_clk

clk_div_reset_ams_n

clk_div_reset_ams_n_r

pll_reconfig_soft_reset_en

pll_reconfig_reset_n

global_or_soft_reset_n