Altera DDR SDRAM High-Performance Controllers and ALTMEMPHY IP User Manual

Page 37

Chapter 3: Parameter Settings

3–11

ALTMEMPHY Parameter Settings

June 2011

Altera Corporation

External Memory Interface Handbook Volume 3

Section I. DDR and DDR2 SDRAM Controllers with ALTMEMPHY IP User Guide

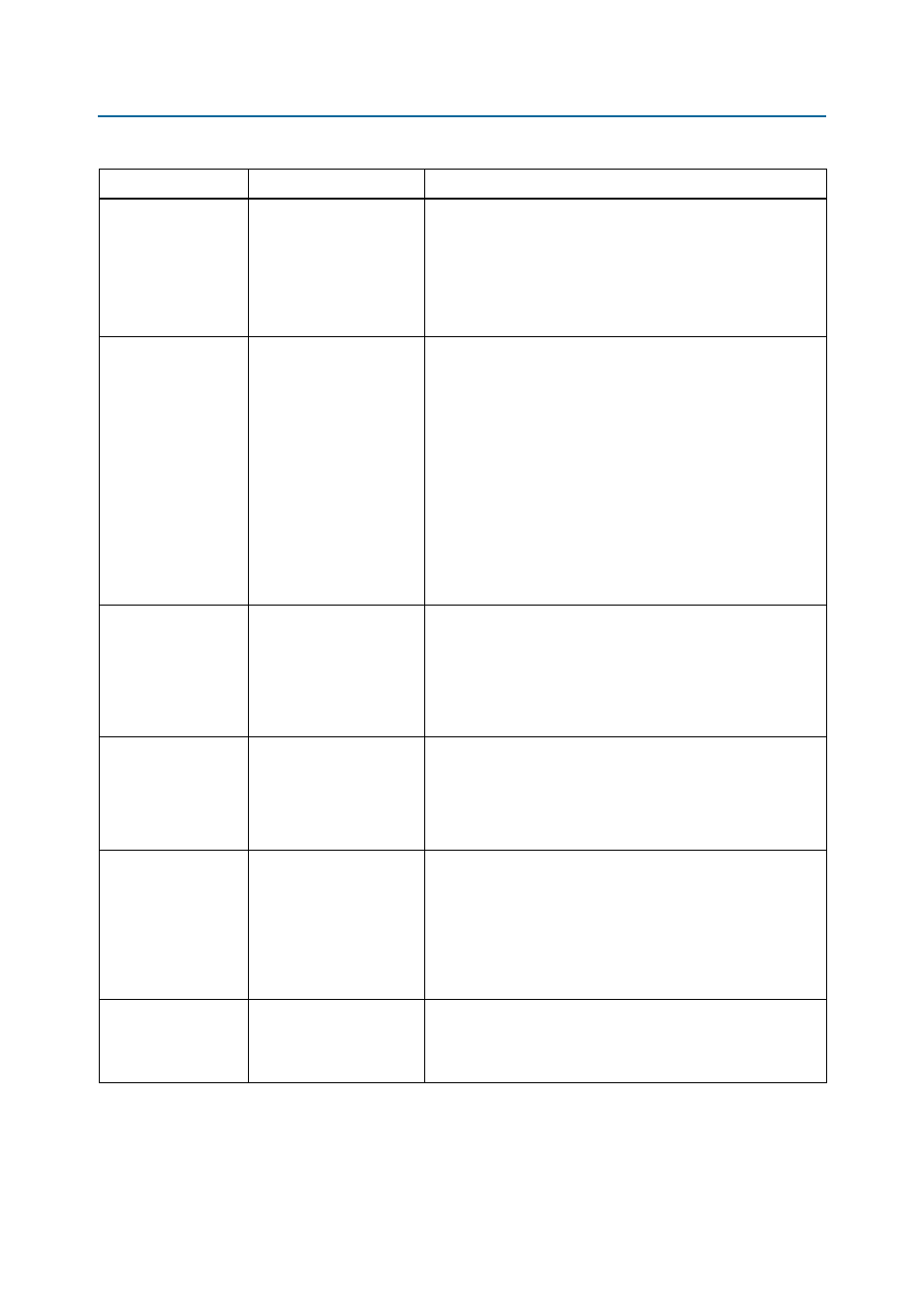

Instantiate DLL

externally

All supported device

families, except for

Cyclone III devices

Use this option with Stratix III, Stratix IV, HardCopy III, or

HardCopy IV devices, if you want to apply a non-standard phase

shift to the DQS capture clock. The ALTMEMPHY DLL offsetting I/O

can then be connected to the external DLL and the Offset Control

Block.

As Cyclone III devices do not have DLLs, this feature is not

supported.

Enable dynamic parallel

on-chip termination

Stratix III and Stratix IV

This option provides I/O impedance matching and termination

capabilities. The ALTMEMPHY megafunction enables parallel

termination during reads and series termination during writes with

this option checked. Only applicable for DDR and DDR2 SDRAM

interfaces where DQ and DQS are bidirectional. Using the dynamic

termination requires that you use the OCT calibration block, which

may impose a restriction on your DQS/DQ pin placements

depending on your R

UP

/R

DN

pin locations.

Although DDR SDRAM does not support ODT, dynamic OCT is still

supported in Altera FPGAs.

For more information, refer to either the

chapter in volume 1 of the Stratix III

Device Handbook or

ter in volume 1 of the Stratix IV Device Handbook.

Clock phase

Arria II GX, Arria GX,

Cyclone III, HardCopy II,

Stratix II, and Stratix II GX

Adjusting the address and command phase can improve the

address and command setup and hold margins at the memory

device to compensate for the propagation delays that vary with

different loadings. You have a choice of 0°, 90°, 180°, and 270°,

based on the rising and falling edge of the phy_clk and

write_clk

signals. In Stratix IV and Stratix III devices, the clock

phase is set to dedicated.

Dedicated clock phase

Stratix III and Stratix IV

When you use a dedicated PLL output for address and command,

you can choose any legal PLL phase shift to improve setup and

hold for the address and command signals. You can set this value

to between 180° and 359°, the default is 240°. However, generally

PHY timing requires a value of greater than 240° for half-rate

designs and 270° for full-rate designs.

Board skew

All supported device

families except Arria II GX

and Stratix IV devices

Maximum skew across any two memory interface signals for the

whole interface from the FPGA to the memory (either a discrete

memory device or a DIMM). This parameter includes all types of

signals (data, strobe, clock, address, and command signals). You

need to input the worst-case skew, whether it is within a DQS/DQ

group, or across all groups, or across the address and command

and clocks signals. This parameter generates the timing constraints

in the .sdc file.

Autocalibration

simulation options

All supported device

families

Choose between Full Calibration (long simulation time), Quick

Calibration, or Skip Calibration.

For more information, refer to

ction in volume 4 of

the External Memory Interface Handbook.

Table 3–6. ALTMEMPHY PHY Settings (Part 2 of 2)

Parameter Name

Applicable Device Families

Description