Altera Arria 10 Avalon-ST User Manual

Page 106

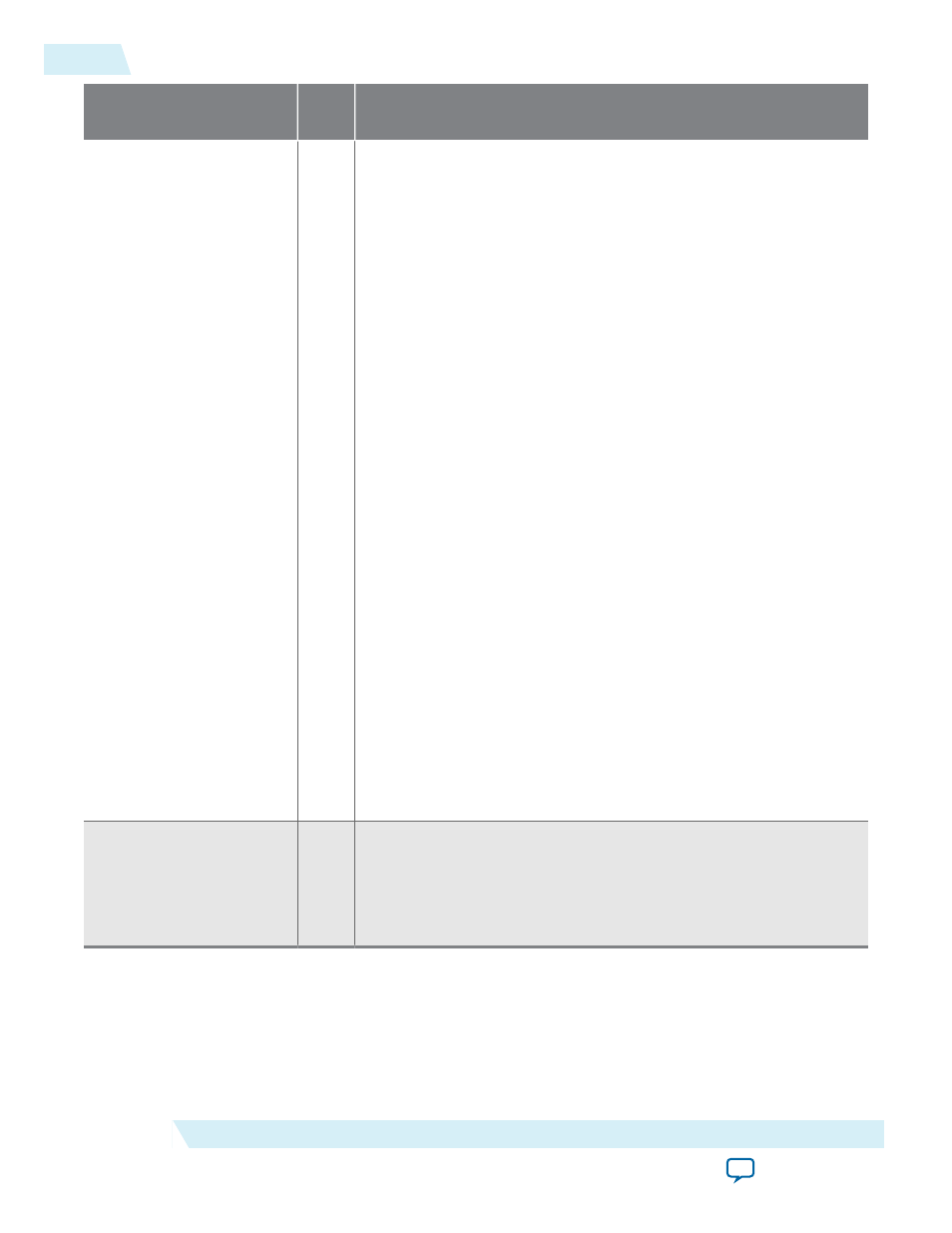

Signal

Directi

on

Description

•

cpl_err[4]

: Unsupported Request (UR) error for posted TLP.

The Application Layer asserts this signal to treat a posted request

as an Unsupported Request. The Hard IP automatically sets the

error status bits in the Configuration Space register and sends

error messages in accordance with the PCI Express Base Specifica‐

tion. Many cases of Unsupported Requests are detected and

reported internally by the Transaction Layer. For a list of these

cases, refer to Transaction Layer Errors.

•

cpl_err[5]

: Unsupported Request error for non-posted TLP. The

Application Layer asserts this signal to respond to a non-posted

request with an Request (UR) completion. In this case, the

Application Layer sends a completion packet with the

Unsupported Request status back to the requestor, and asserts this

error signal. The Hard IP automatically sets the error status bits in

the Configuration Space Register and sends error messages in

accordance with the PCI Express Base Specification. Many cases of

Unsupported Requests are detected and reported internally by the

Transaction Layer. For a list of these cases, refer to Transaction

Layer Errors.

•

cpl_err[6]

: Log header. If header logging is required, this bit

must be set in the every cycle in which any of

cpl_err[2]

,

cpl_

err[3]

,

cpl_err[4]

, or

cpl_err[5]

is set. The Application Layer

presents the header to the Hard IP by writing the following values

to the following 4 registers using LMI before asserting

cpl_

err[6]

:. The Application Layer presents the header to the Hard IP

by writing the following values to the following 4 registers using

LMI before asserting

cpl_err[6]:

• lmi_addr: 12'h81C,

lmi_din

:

err_desc_func0[127:96]

• lmi_addr: 12'h820,

lmi_din

:

err_desc_func0[95:64]

• lmi_addr: 12'h824,

lmi_din

:

err_desc_func0[63:32]

• lmi_addr: 12'h828,

lmi_din

:

err_desc_func0[31:0]

cpl_pending

Input Completion pending. The Application Layer must assert this signal

when a master block is waiting for completion, for example, when a

Non-Posted Request is pending. The state of this input is reflected by

the

Transactions Pending

bit of the

Device Status

Register as

defined in Section 7.8.5 of the PCI Express Base Specification.

Related Information

•

•

PCI Express Base Specification Rev 3.0

6-40

Completion Side Band Signals

UG-01145_avst

2015.05.04

Altera Corporation

Interfaces and Signal Descriptions