Root port mode configuration requests, Clock signals, Reset, status, and link training signals – Altera Arria 10 Avalon-ST User Manual

Page 97: Root port mode configuration requests -31, Clock signals -31, Reset, status, and link training signals -31

Related Information

Tradeoffs to Consider when Enabling Multiple Packets per Cycle

on page 6-15

Root Port Mode Configuration Requests

If your Application Layer implements ECRC forwarding, it should not apply ECRC forwarding to

Configuration Type 0 packets that it issues on the Avalon-ST interface. There should be no ECRC

appended to the TLP, and the

TD

bit in the TLP header should be set to 0. These packets are processed

internally by the Hard IP block and are not transmitted on the PCI Express link.

To ensure proper operation when sending Configuration Type 0 transactions in Root Port mode, the

application should wait for the Configuration Type 0 transaction to be transferred to the Hard IP for PCI

Express Configuration Space before issuing another packet on the Avalon-ST TX port. You can do this by

waiting for the core to respond with a completion on the Avalon-ST RX port before issuing the next

Configuration Type 0 transaction.

Clock Signals

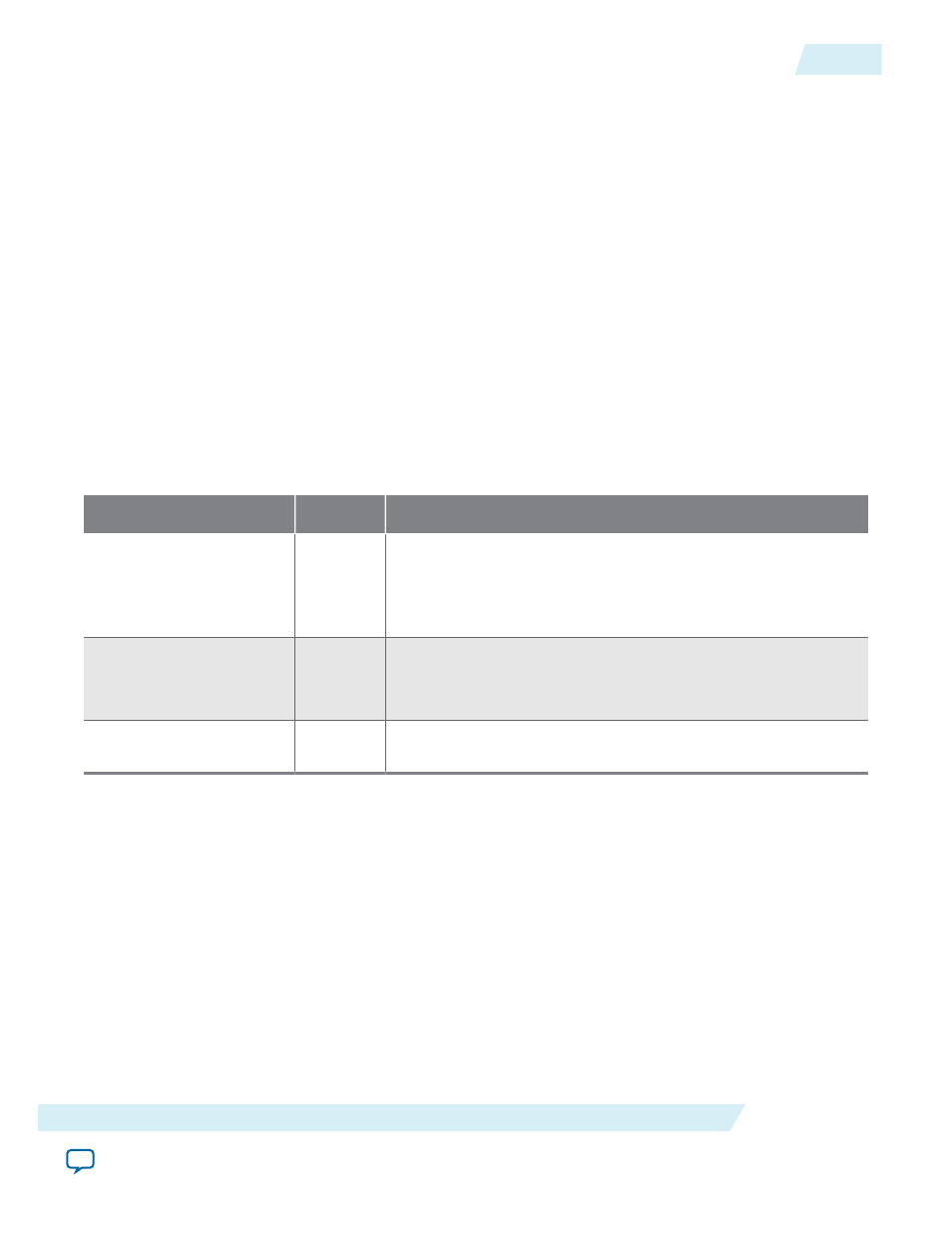

Table 6-5: Clock Signals

Signal

Direction

Description

refclk

Input

Reference clock for the IP core. It must have the frequency

specified under the System Settings heading in the parameter

editor. This is a dedicated free running input clock to the

dedicated

REFCLK

pin.

pld_clk

Input

Clocks the Application Layer. You can drive this clock with

coreclkout_hip

. If you drive

pld_clk

with another clock

source, it must be equal to or faster than

coreclkout_hip

.

coreclkout_hip

Output

This is a fixed frequency clock used by the Data Link and

Transaction Layers.

Related Information

on page 8-4

Reset, Status, and Link Training Signals

Refer to Reset and Clocks for more information about the reset sequence and a block diagram of the reset

logic.

UG-01145_avst

2015.05.04

Root Port Mode Configuration Requests

6-31

Interfaces and Signal Descriptions

Altera Corporation