Altera Arria 10 Avalon-ST User Manual

Page 37

Advertising

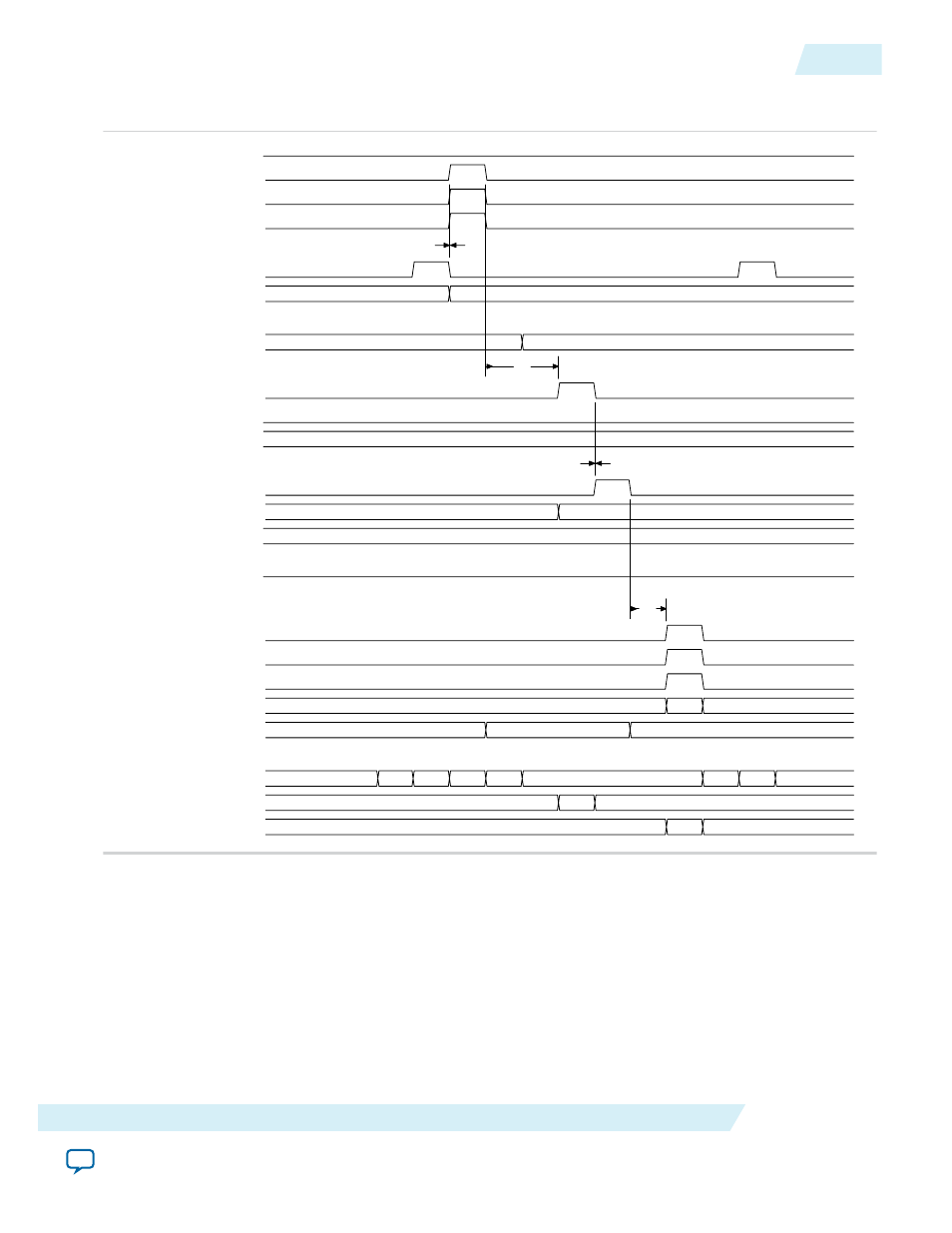

Figure 3-4: Configuration Read to Function 0

RxStMask_o

RxStSop_i

RxStEop_i

RxStValid_i

RxStReady_o

RxStData_i[255:0]

cfg_addr_o[31:0]

cfg_rden_o

cfg_wren_o

cfg_be_o[3:0

cfg_rddatavalid

_

cfg_rddata_i[31:0]

cfg_readresponse_i[2:0]

TxStReady_i

TxStSop_o

TxStEop_o

TxStValid_o

TxStEmpty_o[1:0]

TxStData_o[255:0]

rx_state[10:0]

rxcfg_state[4:0]

tx_state[1:0]

1

’b0000000000000000000

.

000

003

005

021

009

000

E0011172

...E00111720000000000000044A000001

01080000

01120004

05

3

1

2

3

4

UG-01145_avst

2014.08.18

Timing for Configuration Read to Function 0 for the 256-Bit Avalon-ST Interface

3-7

Getting Started with the Configuration Space Bypass Mode Qsys Example Design

Altera Corporation

Advertising