Altera Arria 10 Avalon-ST User Manual

Page 92

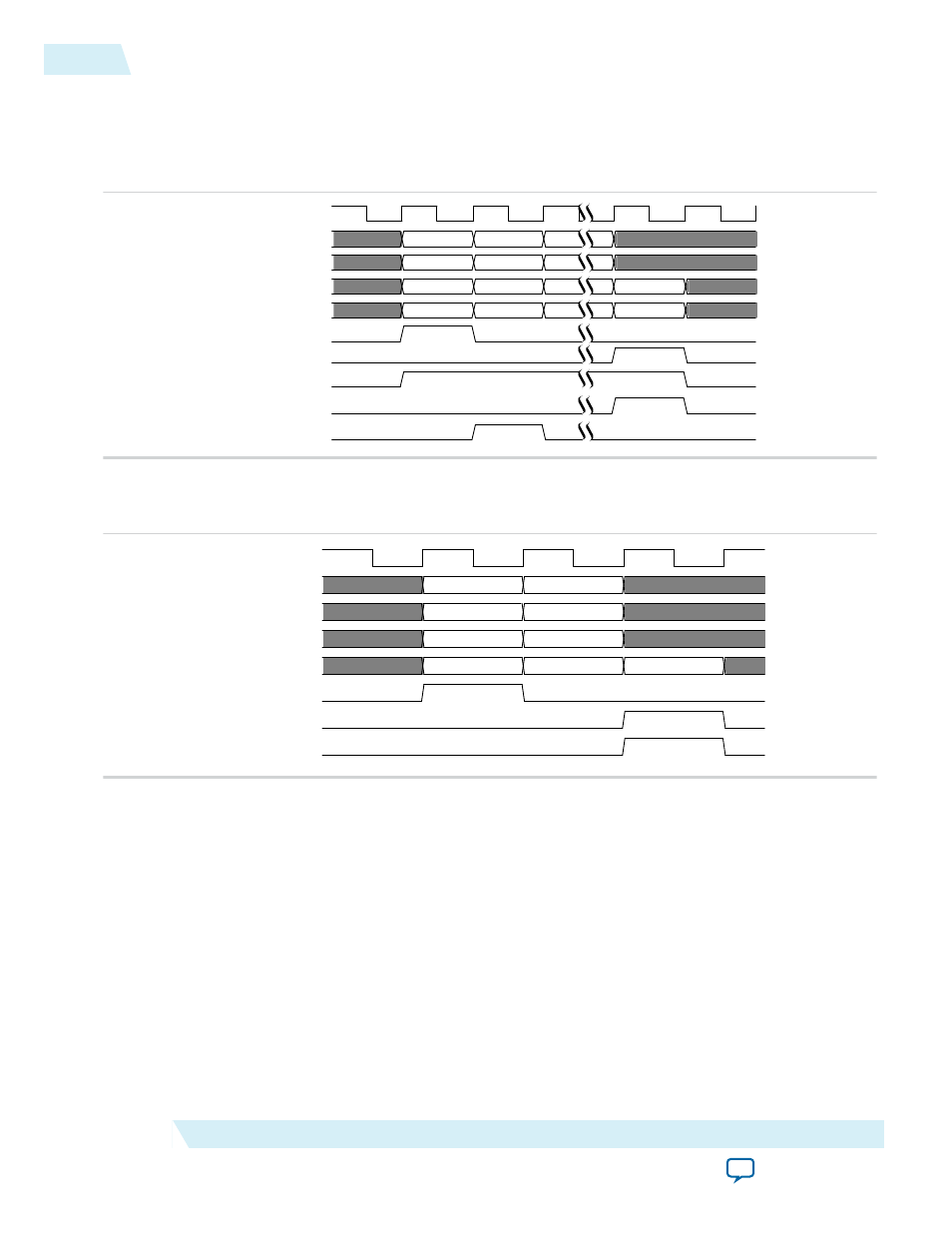

Figure 6-25: 128-Bit Avalon-ST tx_st_data Cycle Definition for 3-Dword Header TLP with non-Qword

Aligned Address

The following figure shows the mapping of 128-bit Avalon-ST TX packets to PCI Express TLPs for a 3

dword header with non-qword aligned addresses. It also shows

tx_st_err

assertion.

pld_clk

tx_st_valid

tx_st_data[127:96]

tx_st_data[95:64]

tx_st_data[63:32]

tx_st_data[31:0]

tx_st_sop

tx_st_err

tx_st_eop

tx_st_empty

Data0

Data 4

Header 2

Data 3

Header 1

Data 2

Data (n)

Header 0

Data 1

Data (n-1)

Figure 6-26: 128-Bit Avalon-ST tx_st_data Cycle Definition for 4-Dword Header TLP with Qword

Aligned Address

pld_clk

tx_st_data[127:96]

tx_st_data[95:64]

tx_st_data[63:32]

tx_st_data[31:0]

tx_st_sop

tx_st_eop

tx_st_empty

Header 3

Data 3

Header 2

Data 2

Header 1

Data 1

Header 0

Data 0

Data 4

Figure 6-27: 128-Bit Avalon-ST tx_st_data Cycle Definition for 4-Dword Header TLP with non-Qword

Aligned Address

The following figure shows the mapping of 128-bit Avalon-ST TX packets to PCI Express TLPs for a four

dword header TLP with non-qword aligned addresses. In this example,

tx_st_empty

is low because the

data ends in the upper 64 bits of

tx_st_data

.

6-26

Data Alignment and Timing for the 128‑Bit Avalon‑ST TX Interface

UG-01145_avst

2015.05.04

Altera Corporation

Interfaces and Signal Descriptions