Altera Arria 10 Avalon-ST User Manual

Page 172

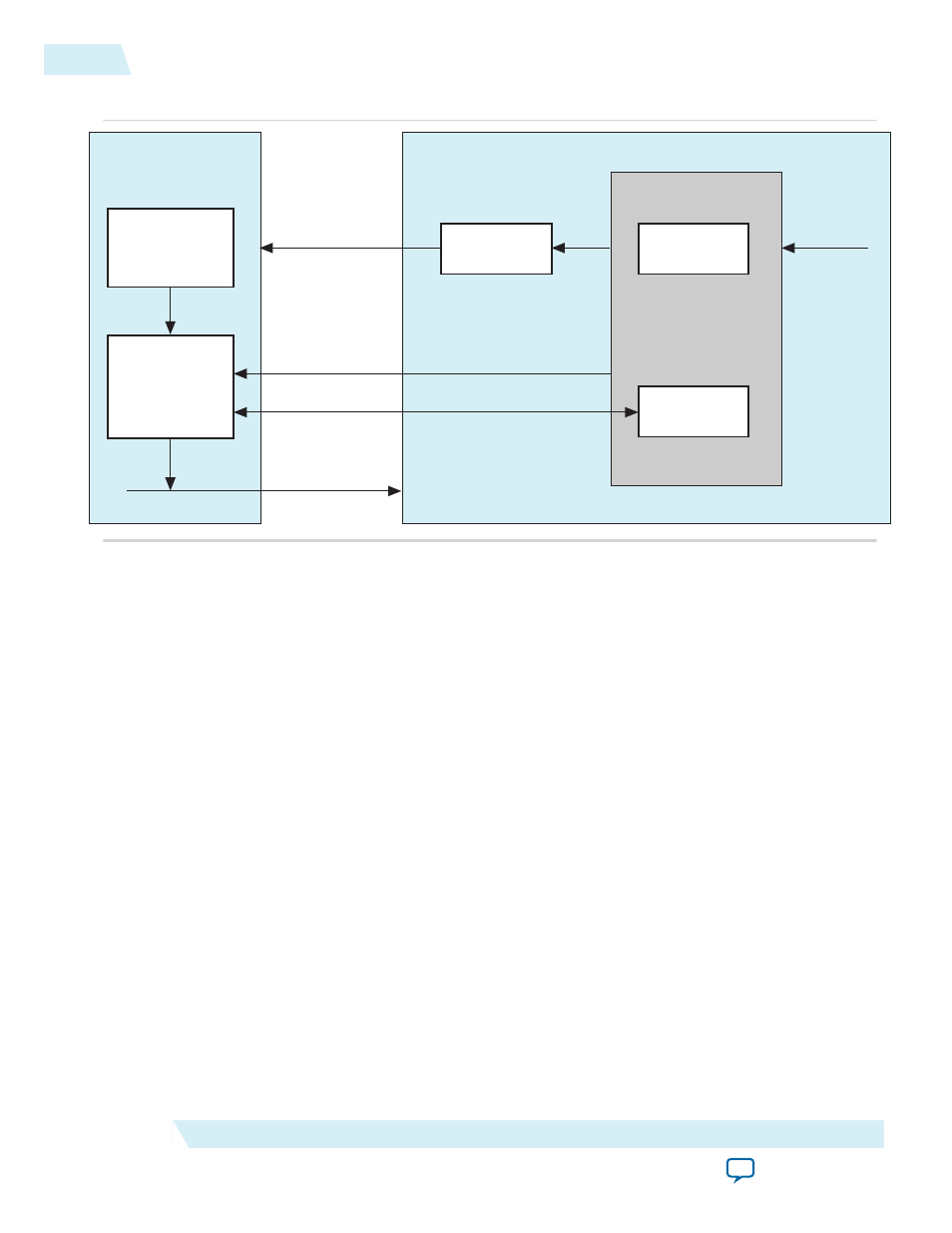

Figure 11-3: Error Handing in Configuration Space Bypass Mode

Transaction Layer of the Hard IP for PCI Express

Application Layer

(Soft Logic)

Avalon-ST TX

Custom Configuration

Space

and Error Handling

Error Detect (Corrected Errs,

Malformed TLPs)

RX Buffer &

Flow Control

Avalon-ST RX

Real-Time Error Flags

(Malformed, Corrected)

LMI

Config TLPs

Errors

Completions,

Messages

Error Detect

(UR, Unexpected

Completion)

Drop Malformed

TLPs

AER Registers

The following list summarizes the behavior of the Transaction Layer error handling in Configuration

Space Bypass Mode:

• The Translation Layer discards malformed TLPs. The

err_tlmalf

output signal is asserted to indicate

this error. The Transaction Layer also logs this error in the

Uncorrectable Error Status

,

AER

Header Log

, and

First Error Pointer

Registers

. The Transaction Layer’s definition of malformed

TLPs is same in normal and Configuration Space Bypass modes.

• Unsupported Requests are not recognized by the Transaction Layer. The Application Layer must

identify unsupported requests.

• Unexpected completions are not recognized by the Transaction Layer. The Application Layer must

identify unexpected completions.

• You can use the Transaction Layer’s ECRC checker in Configuration Space Bypass mode. If you enable

ECRC checking with the

r

x_ecrcchk_pld

input signal and the Transaction Layer detects an ECRC

error, the Transaction Layer asserts the

rx_st_ecrcerr

output signal with the TLP on the Avalon-ST

RX interface. The Application Layer must handle the error. If ECRC generation is enabled, the core

generates ECRC and appends it to the end of the TX TLP from the Application Layer. Refer to

Table 12–1 on page 12–2 and Table 12–2 on page 12–3 for additional information.

11-8

Error Checking and Handling in Configuration Space Bypass Mode

UG-01145_avst

2014.08.18

Altera Corporation

IP Core Architecture